# Course Material on Switched Mode Power Conversion

Department of Electrical Engineering Indian Institute of Science Bangalore 560012 (for Private Circulation Only)

V. Ramanarayanan

January 15, 2008

© V. Ramanarayanan 2005 First Edition 2005 Second Edition 2006

# Preface

Power electronics forms an important part of industrial electronics. Power electronics is defined as the application of electronic devices and associated components to the efficient conversion, control and conditioning of electric power. The modern power electronics technology traces its origin to the technology of rectifiers developed using mercury arc devices. From this beginning of simple ac-dc conversion of power, today the technology has grown to encompass the general definition given above. The conversion of power relates to the form of electric power namely ac or dc. The control application relates to the regulation of electrical quantities like voltage, current, power etc. or the regulation of non-electrical quantities such as the speed of a motor, the temperature in an oven, the intensity of lighting etc. The conditioning of electrical power relates to the quality of power quantified through harmonic content, reactive power in a system and so on.

The key aspect of power electronics is the efficiency of power processing. As bulk power is processed in power electronic systems, high efficiency of power conversion is vital for reasons of both the economic value of lost power as well as the detrimental effect of the heat that the lost power results in a power electronic system.

Traditionally the subject of power electronics is introduced in an undergraduate curriculam more as "Thyristor and its applications" than as the subject of power electronics proper [1]. The reason for this bias is understandable. Historically the first commercial solid state power switching device available was the silicon controlled rectifier (SCR). Initially the SCRs started replacing the ignitron tubes for ac-dc conversion and Ward-Leonard systems for the speed control of dc motors. With the availability of fast SCRs, the application of SCRs entered the area of dc-ac power conversion as well. The subject of power electronics practically grew with the application of SCRs. The undergraduate curriculum therefore centered around the SCR and broadly dealt with naturally commutated converters for ac-dc power conversion, and forced commutated converters for the dc-ac power converters [8]. The application area was broadly classified into natural commutated applications and forced commutated applications. This classification itself grew out of the limitation of the SCR that it cannot be turned off through the control gate. The focus of such a curriculum was on the SCR in the centre and its myriad applications based on the above classification.

However the monopoly of SCR as the power electronic switch was eroded from the mid 1970s. The newer devices arriving in the commercial scene were bipolar junction transistor (BJT), metal oxide semiconductor field effect transistor (MOSFET), and the insulated gate bipolar transistor (IGBT). These devices are fully controllable (both off/on transition and on/off transition), faster in switching, and easier to control compared to the SCR. These modern devices are getting closer and closer to the ideal properties of a switch. The classification of applications based on the property of SCR (natural/forced commutation) has become dated.

Accordingly a curriculum addressing the under-graduate students under the title Switched Mode Power Conversion is presented in this book [14]. This is a sub-set of the broad subject matter of power electronics.

The subject matter is covered starting from the properties of ideal switches, real power semiconductor switches and their idealisation, realisation of different circuit topologies, thier operation, steady state performance, dynamic properties, analysis methods, idealised models, effect of non-idealities, control strategies, application of feedback and feedforward control to achieve overall performance and so on. This may be taken as a first course on Switched mode power conversion. The material covered are as follows.

- Power Switching Elements

- Reactive Elements in Power Electronic Systems

- Control, Drive and Protection of Power Switching Devices

- DC-DC Converters

- DC-DC Converters Dynamics

- Closed Loop Control of Power Converters

- Current Programmed Converters

- Soft Switching Converters

- Unity Power Factor Rectifiers

Each chapter has a full complement of exercises and a problem set. Advanced topics such as active filters, and simulation techniques applied to power converters will be topics covered in the next edition of this book

Subject material such as Switched Mode Power Conversion is an application subject. It will be very valuable to include in such a text book design examples and data sheets of power switching devices, magnetic materials, control ICs, manufacturer's application notes etc. This has been done and the material has been designed in the pdf format with links to all the necessary resource material embedded in the same. The appendices carry a number of sections which will enhance the understanding of the subject matter.

V. Ramanarayanan vram@ee.iisc.ernet.in Department of Electrial Engineering Indian Institute of Science 560012

# Contents

| 1 | Pow  | ver Switching Devices - Characteristics                                                           | 1  |

|---|------|---------------------------------------------------------------------------------------------------|----|

|   | 1.1  | Introduction                                                                                      | 1  |

|   | 1.2  | Ideal Switches                                                                                    | 2  |

|   | 1.3  | Real Switches                                                                                     | 3  |

|   | 1.4  | Practical Power Switching Devices                                                                 | 4  |

|   | 1.5  | Diodes                                                                                            | 6  |

|   |      | 1.5.1 Schottky diodes                                                                             | 8  |

|   |      | 1.5.2 Rectifier diodes                                                                            | 8  |

|   |      | 1.5.3 Fast diodes                                                                                 | 8  |

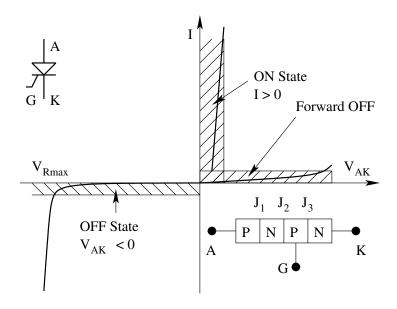

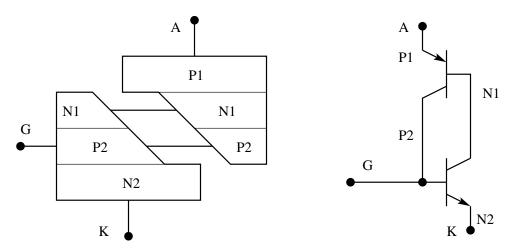

|   | 1.6  | Thyristor or Silicon Controlled Rectifier (SCR)                                                   | 9  |

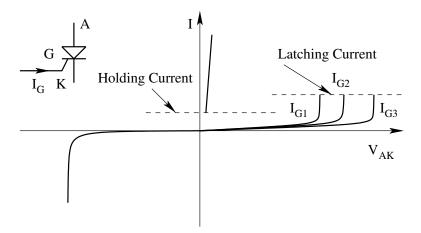

|   |      | 1.6.1 Gate turn-on                                                                                | 9  |

|   |      | 1.6.2 Voltage turn-on                                                                             | 10 |

|   |      | 1.6.3 $dV/dt$ turn-on                                                                             | 10 |

|   |      | 1.6.4 Temperature effect                                                                          | 10 |

|   |      | 1.6.5 Light firing                                                                                | 10 |

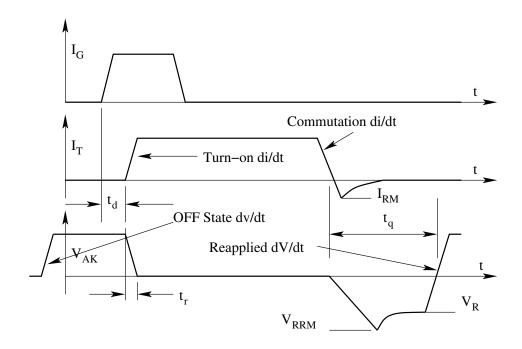

|   |      | 1.6.6 Turn-off of an SCR                                                                          | 11 |

|   |      | 1.6.7 Switching Characteristics of the SCR                                                        | 11 |

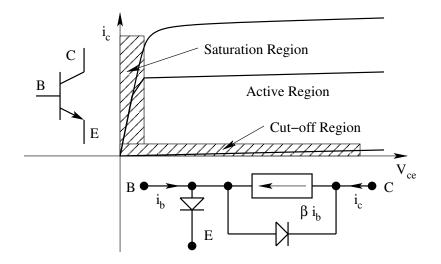

|   | 1.7  | Bipolar Junction Transistor (BJT)                                                                 | 14 |

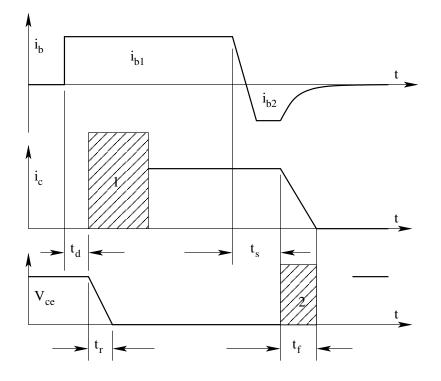

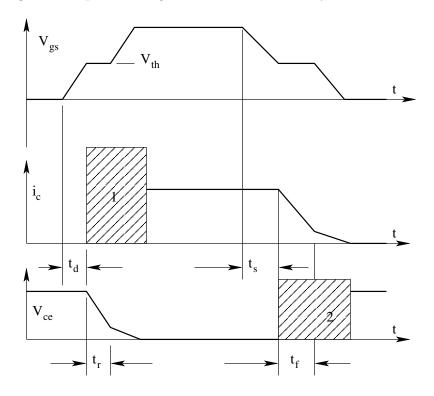

|   |      | 1.7.1 Switching Characteristics of the Transistor                                                 | 15 |

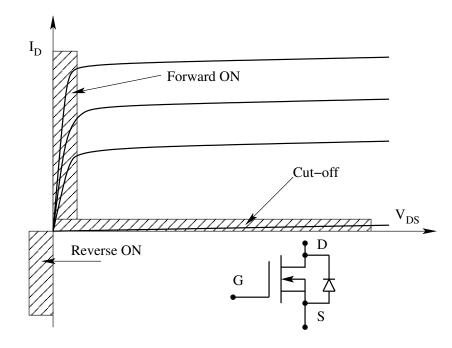

|   | 1.8  | MOS Field Effect Transistor(MOSFET)                                                               | 16 |

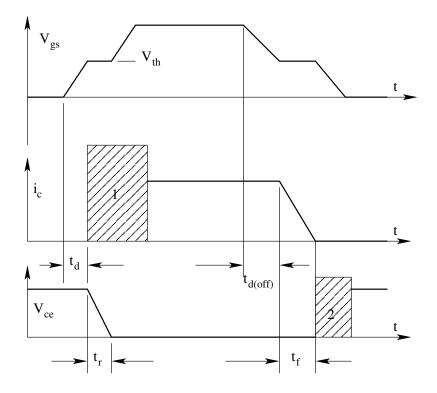

|   |      | 1.8.1 Switching Charcteristics of the MOSFET                                                      | 18 |

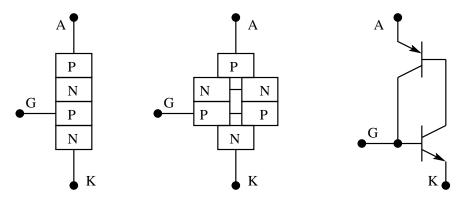

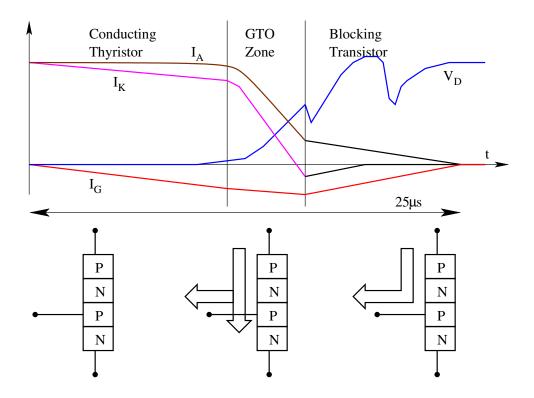

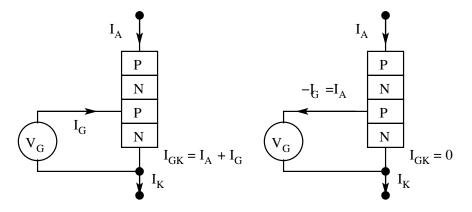

|   | 1.9  | Gate Turn-off Thyristor (GTO)                                                                     | 19 |

|   |      | 1.9.1 Turn-on                                                                                     | 20 |

|   |      | 1.9.2 Conduction $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 21 |

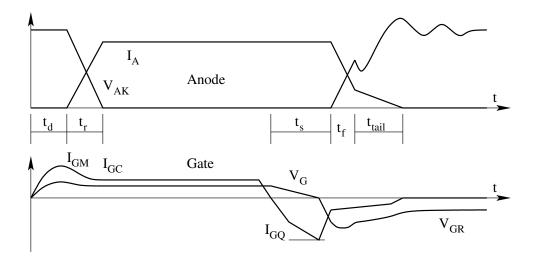

|   |      | 1.9.3 Turn-off                                                                                    | 21 |

|   |      | 1.9.4 Blocking                                                                                    | 22 |

|   |      | 1.9.5 Gate Drive                                                                                  | 22 |

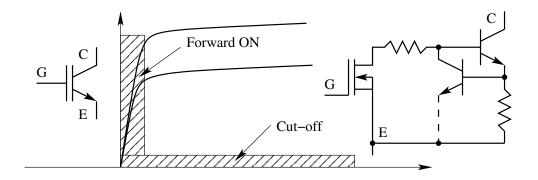

|   | 1.10 | Insulated Gate Bipolar Transistor (IGBT)                                                          | 23 |

|   |      | 1.10.1 Switching Characteristics of the IGBT                                                      | 25 |

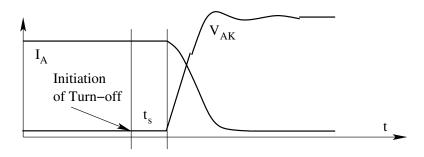

|   | 1.11 | Integrated Gate Commutated Thyristor (IGCT)                                                       | 26 |

|   |      | Comparisons                                                                                       | 28 |

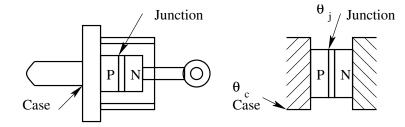

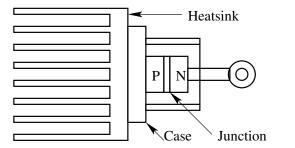

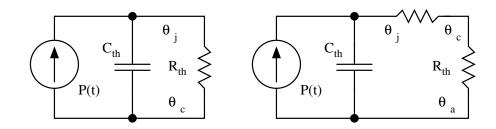

|   | 1.13 | Thermal Design of Power Switching Devices                                                         | 28 |

|   |      | 1.13.1 Thermal model of the device                                                                | 29 |

|          |      | 1.13.2   | Steady state temperature rise                                                                                                                    |

|----------|------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------|

|          |      |          | Transient temperature rise                                                                                                                       |

|          |      |          | Equivalent circuit of the thermal model                                                                                                          |

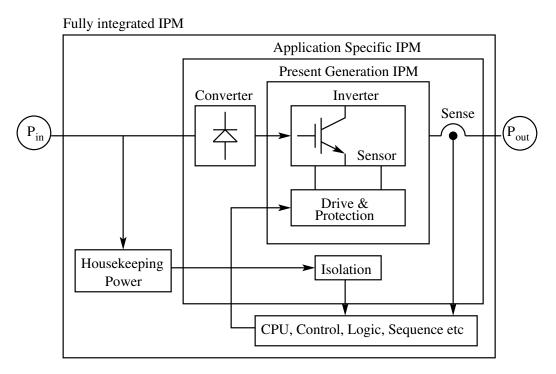

|          | 1.14 |          | ent Power Modules (IPM)                                                                                                                          |

|          |      |          | ted Examples                                                                                                                                     |

|          |      |          | $m \text{ Set } \dots $                    |

|          |      |          |                                                                                                                                                  |

| <b>2</b> | Rea  |          | Elements in Power Electronic Systems 47                                                                                                          |

|          | 2.1  |          | action $\ldots \ldots 47$                             |

|          | 2.2  | Electro  | magnetics $\ldots \ldots 47$                                        |

|          | 2.3  | Design   | of Inductor                                                                                                                                      |

|          |      | 2.3.1    | $Material \ constraints \ \ \ldots \ \ \ldots \ \ \ldots \ \ 51$                                                                                 |

|          |      | 2.3.2    | Design Relationships                                                                                                                             |

|          |      | 2.3.3    | Design steps $\ldots \ldots 52$                       |

|          | 2.4  | Design   | of Transformer $\ldots \ldots 54$                                                 |

|          |      | 2.4.1    | Design Steps                                                                                                                                     |

|          |      | 2.4.2    | Transformer and Choke Design Table                                                                                                               |

|          | 2.5  |          | tors for Power Electronic Application                                                                                                            |

|          | 2.6  | Types of | of Capacitors                                                                                                                                    |

|          |      | 2.6.1    | Coupling Capacitors                                                                                                                              |

|          |      | 2.6.2    | Power capacitors (low frequency) 58                                                                                                              |

|          |      |          | Power capacitors (high frequency)                                                                                                                |

|          |      |          | Filter capacitors                                                                                                                                |

|          |      |          | Pulse capacitors                                                                                                                                 |

|          |      | 2.6.6    | Damping capacitors                                                                                                                               |

|          |      | 2.6.7    | Commutation capacitors                                                                                                                           |

|          |      | 2.6.8    | Resonant capacitors                                                                                                                              |

|          | 2.7  | Illustra | ted Examples                                                                                                                                     |

|          | -    |          |                                                                                                                                                  |

| 3        |      |          | rive and Protection of Power Switching Devices 69                                                                                                |

|          | 3.1  |          | $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                             |

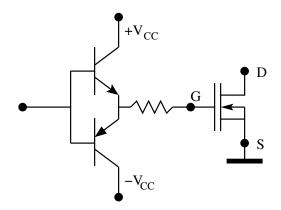

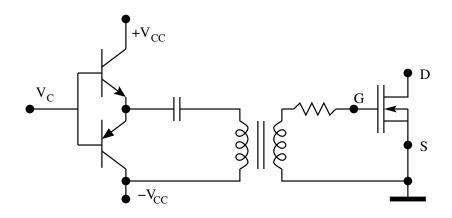

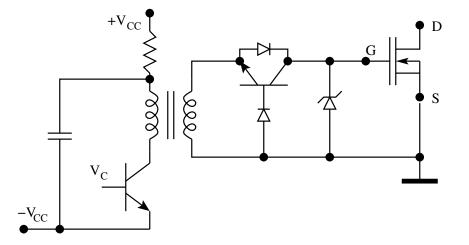

|          | 3.2  |          | prive Circuits for BJT                                                                                                                           |

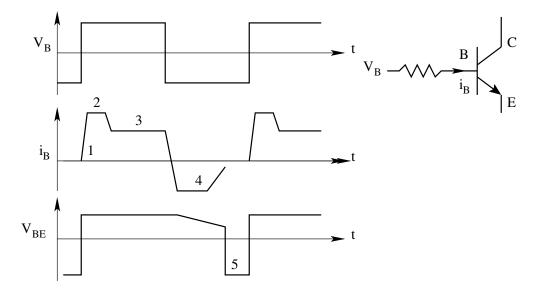

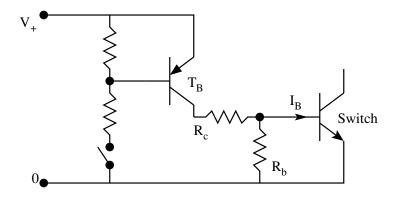

|          |      |          | Requirements of Base Drive                                                                                                                       |

|          |      | 3.2.2    | Drive Circuit 1                                                                                                                                  |

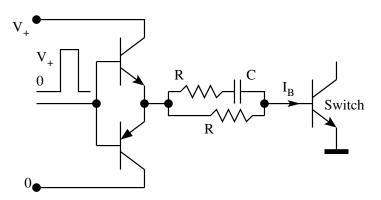

|          |      |          | Drive Circuit 2                                                                                                                                  |

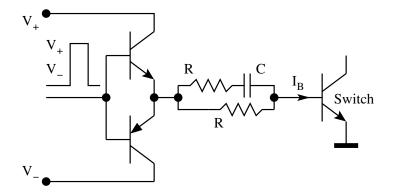

|          |      |          | Drive Circuit $3 \ldots $ |

|          |      |          | Drive Circuit 4 $\ldots \ldots $ |

|          |      |          | Drive Circuit 5 $\ldots \ldots 74$                                                |

|          |      |          | Drive Circuit $6 \ldots 74$                                                |

|          |      |          | Drive Circuit 7                                                                                                                                  |

|          |      |          | Drive Circuit 8                                                                                                                                  |

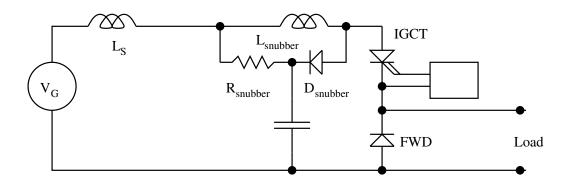

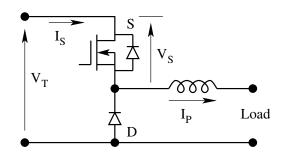

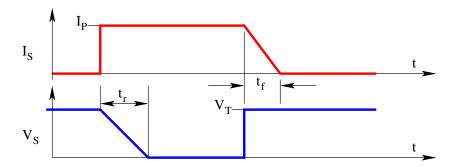

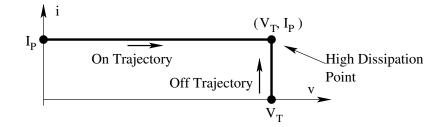

|          | 3.3  | Snubbe   | er Circuits for Power Switching Devices                                                                                                          |

|          |      | 3.3.1    | Turn-off Snubber                                                                                                                                 |

|          |      | 3.3.2    | Turn-on Snubber                                                                                                                                  |

# CONTENTS

|          | 3.4 | Gate Drive Circuits for MOSFET                         | 82       |

|----------|-----|--------------------------------------------------------|----------|

|          |     | 3.4.1 Requirements of Gate Drive                       | 82       |

|          | 3.5 | Illustrated Examples                                   | 86       |

| 4        | DC  | -TO-DC Converter                                       | 05       |

| 4        | _   |                                                        | 95<br>05 |

|          | 4.1 | Introduction                                           | 95<br>06 |

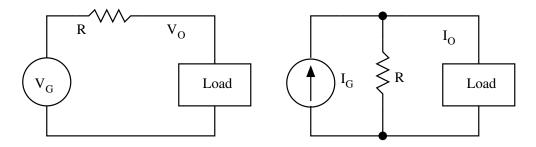

|          | 4.2 | Simple DC to DC Converter                              | 96       |

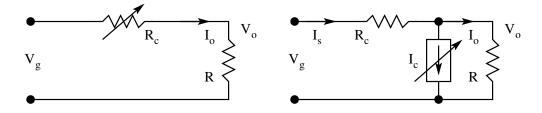

|          |     | 4.2.1 Series Controlled Regulator                      | 97       |

|          |     | 4.2.2 Shunt Controlled Converter                       | 97       |

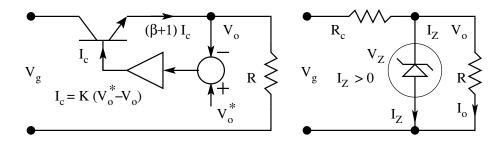

|          |     | 4.2.3 Practical Regulators                             | 98       |

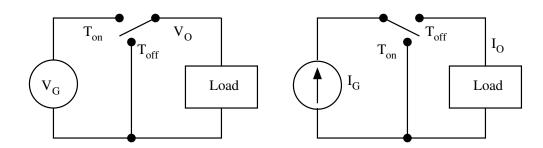

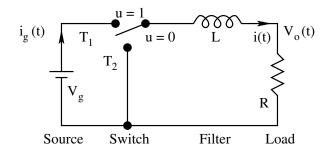

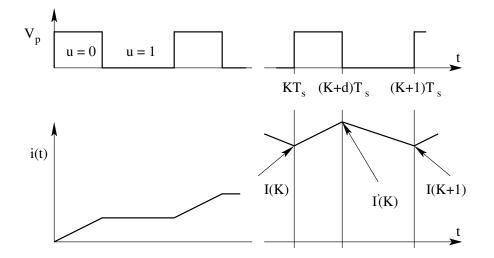

|          | 4.3 | Switched Mode Power Converters                         | 99       |

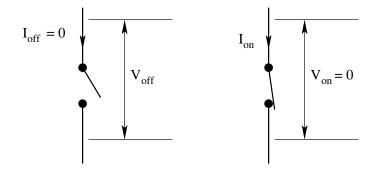

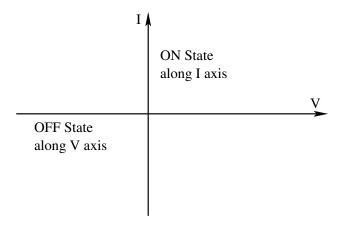

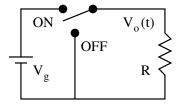

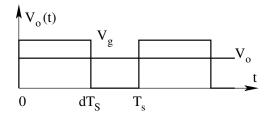

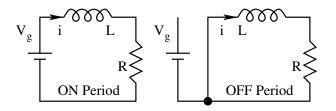

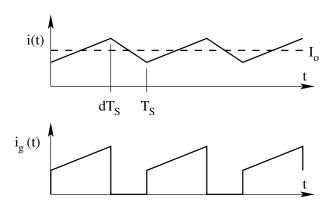

|          |     | 4.3.1 Primitive dc-to-dc Converter                     | 100      |

|          |     | 4.3.2 A Simplified Analysis Of The Primitive Converter | 104      |

|          |     | 4.3.3 Nonidealities in the Primitive Converters:       | 106      |

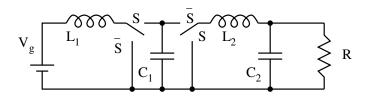

|          | 4.4 | More Versatile Power Converters                        | 107      |

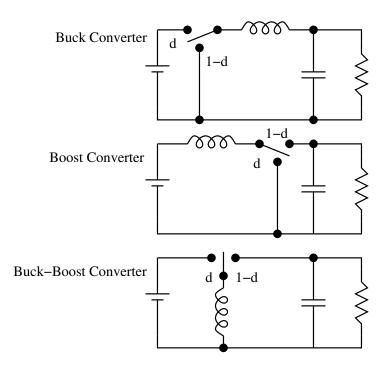

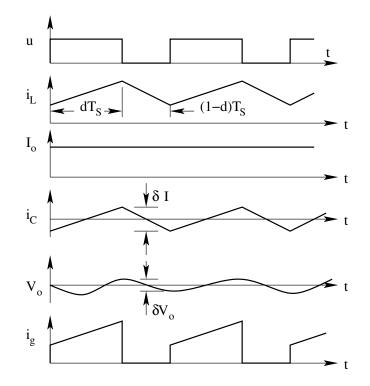

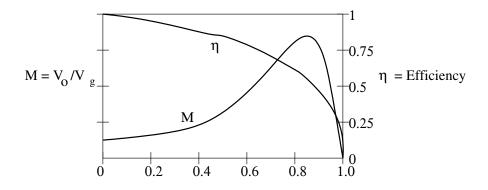

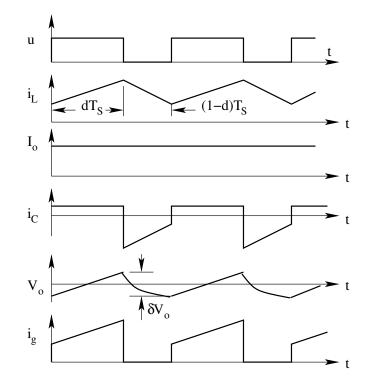

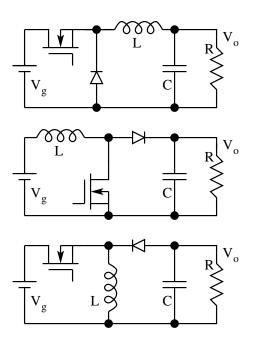

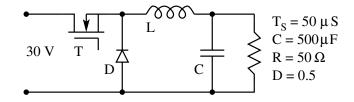

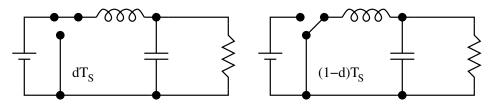

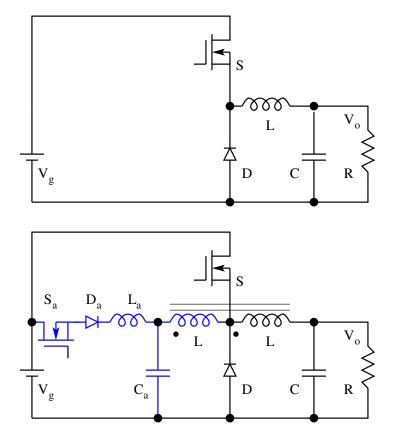

|          |     | 4.4.1 Buck Converter                                   | 108      |

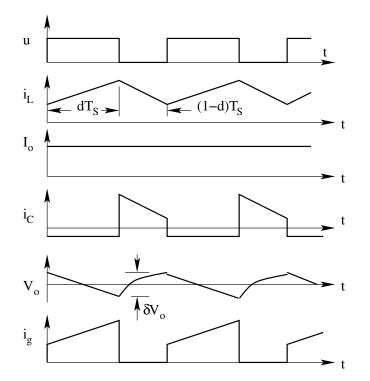

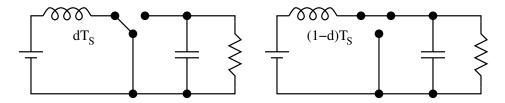

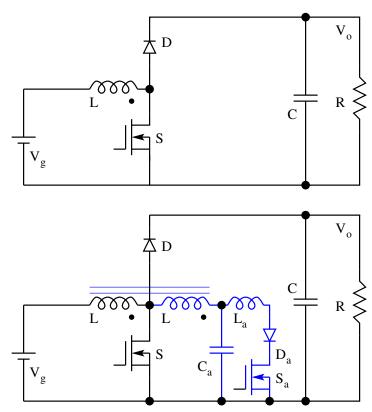

|          |     | 4.4.2 Boost Converter                                  | 110      |

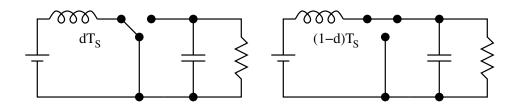

|          |     | 4.4.3 Buck-Boost Converter                             | 112      |

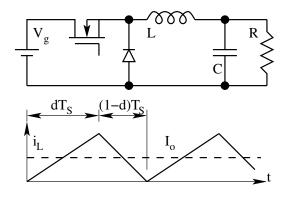

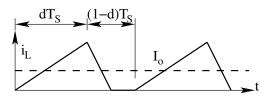

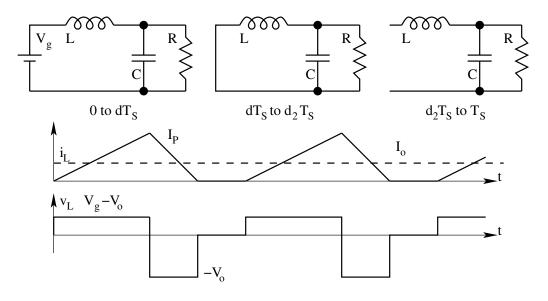

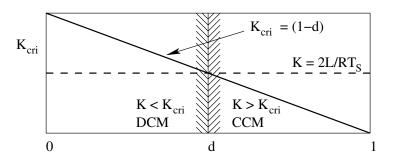

|          | 4.5 | Discontinuous Mode of Operation in dc to dc Converters | 115      |

|          |     | 4.5.1 Buck converter in DCM Operation                  | 117      |

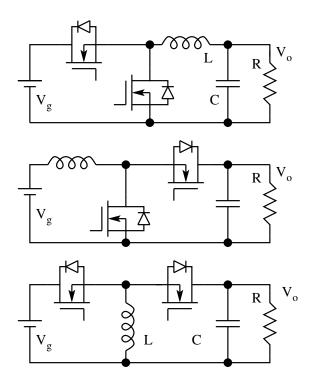

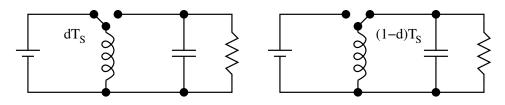

|          | 4.6 | Isolated dc to dc Converters                           | 122      |

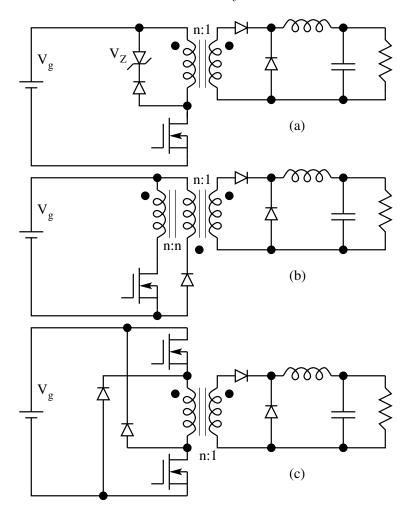

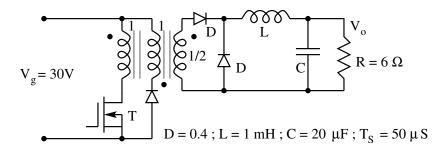

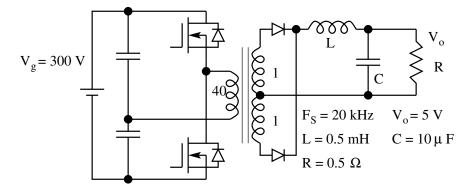

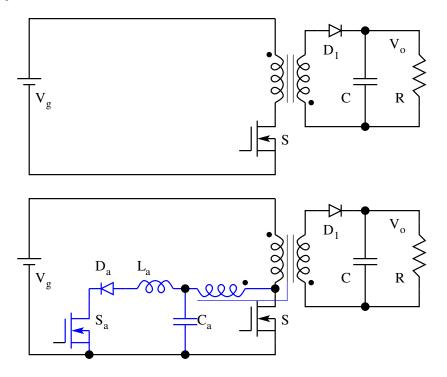

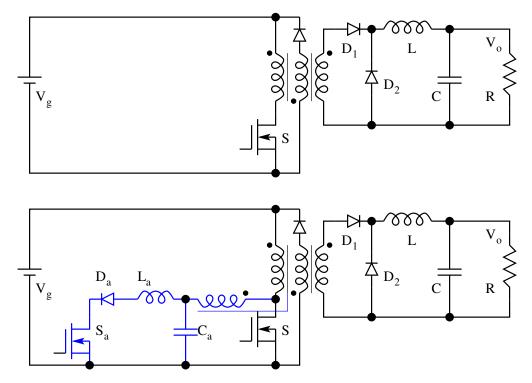

|          |     | 4.6.1 Forward Converter                                | 123      |

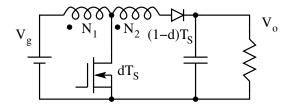

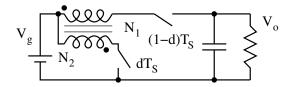

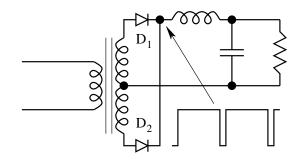

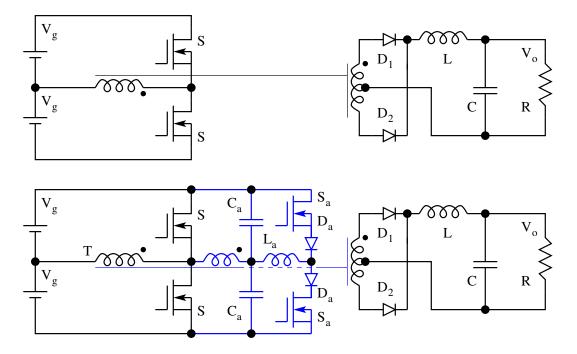

|          |     | 4.6.2 Push-Pull converter                              | 124      |

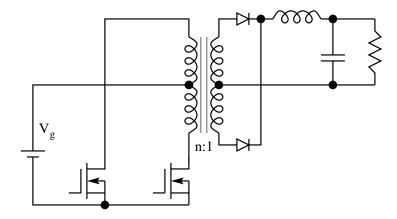

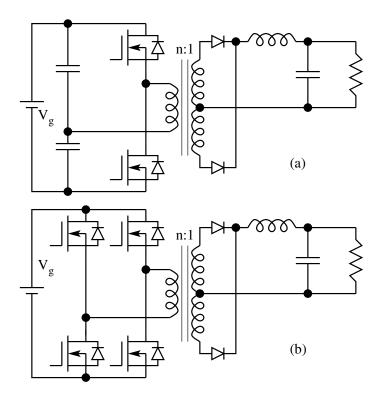

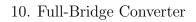

|          |     | 4.6.3 Half and Full Bridge Converter                   | 124      |

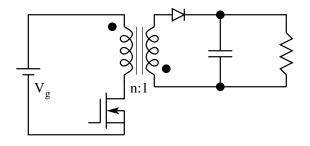

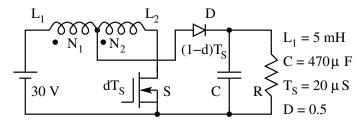

|          |     | 4.6.4 Fly-back Converter                               | 126      |

|          | 4.7 | Problem Set                                            | 126      |

|          |     |                                                        |          |

| <b>5</b> |     | -TO-DC Converter – Dynamics                            | 135      |

|          | 5.1 | Introduction                                           | 135      |

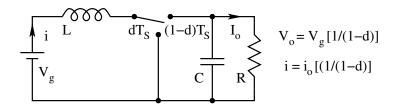

|          | 5.2 | Pulse Width Modulated Converter                        | 136      |

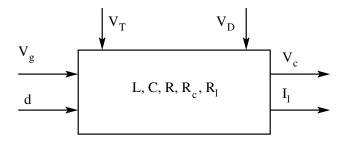

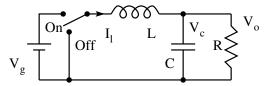

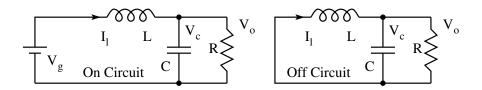

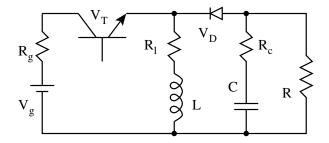

|          |     | 5.2.1 Dynamic and Output Equations of the Converter    | 137      |

|          | 5.3 | An Idealized Example                                   | 138      |

|          | 5.4 | A More Realistic Example                               | 140      |

|          | 5.5 | Averaged Model of the Converter                        | 142      |

|          |     | 5.5.1 Steady State Solution                            | 143      |

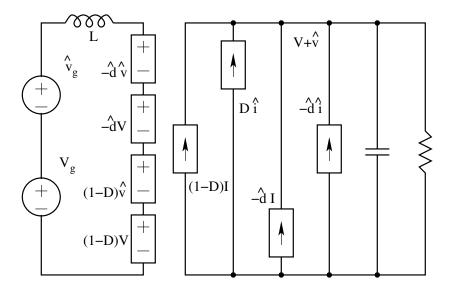

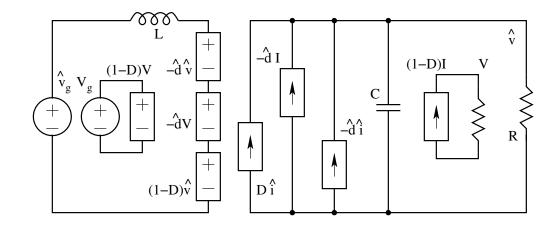

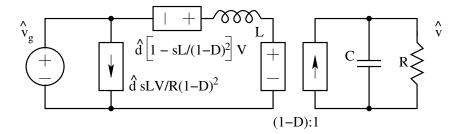

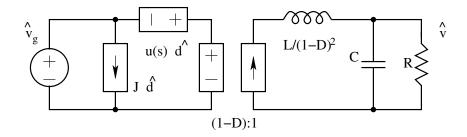

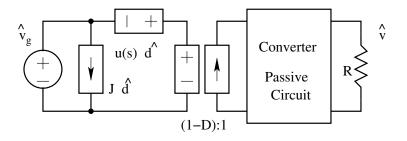

|          |     | 5.5.2 Small Signal Model of The Converter              | 146      |

|          |     | 5.5.3 Transfer Functions of the converter              | 147      |

|          |     | 5.5.4 Example of a Boost Converter                     | 149      |

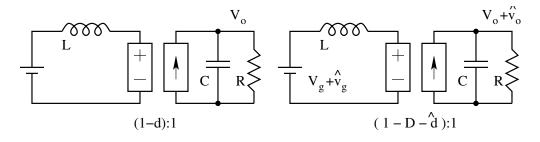

|          | 5.6 | Circuit Averaged Model of the Converters               | 152      |

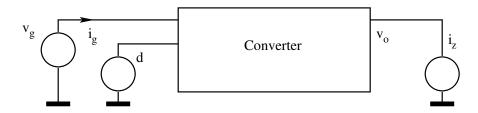

|          | 5.7 | Generalised State Space Model of the Converter         | 155      |

|          |     | 5.7.1 Generalised Model                                | 156      |

|          |     | 5.7.2 Linear Small signal Model                        | 157      |

|          |     | 5.7.3 Dynamic functions of the Converter               | 157      |

|          |     | 5.7.4 Circuit Averaged Model Quantities                | 158      |

|          |     | ~ •                                                    |          |

|          | 5.8  | Some Examples                                              | 159 |

|----------|------|------------------------------------------------------------|-----|

|          |      | 5.8.1 Buck Converter:                                      | 159 |

|          |      | 5.8.2 Boost Converter                                      | 160 |

|          |      |                                                            | 162 |

|          | 5.9  |                                                            | 163 |

|          |      | · · · ·                                                    | 163 |

|          |      |                                                            | 165 |

|          | 5.10 | 0 I                                                        | 167 |

|          | 0.10 |                                                            | 101 |

| 6        | Clo  | sed Loop Control of Power Converters                       | 79  |

|          | 6.1  |                                                            | 179 |

|          | 6.2  | Closed Loop Control                                        | 179 |

|          |      | 6.2.1 Control Requirements                                 | 179 |

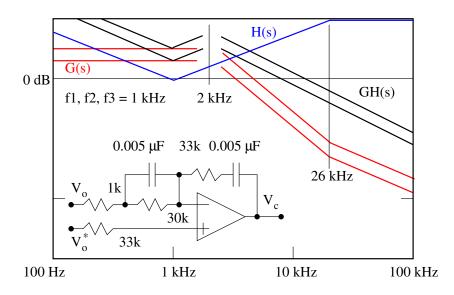

|          |      | 6.2.2 Compensator Structure                                | 180 |

|          |      | 6.2.3 Design of Compensator                                | 180 |

|          |      |                                                            | 182 |

|          | 6.3  | Closed Loop Performance Functions                          | 184 |

|          |      |                                                            | 185 |

|          |      |                                                            | 186 |

|          |      |                                                            | 186 |

|          | 6.4  |                                                            | 187 |

|          | 6.5  | -                                                          | 193 |

|          |      | ° ·                                                        | 193 |

|          | 6.6  | Ç İ                                                        | 197 |

|          |      |                                                            |     |

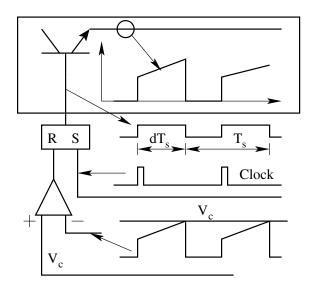

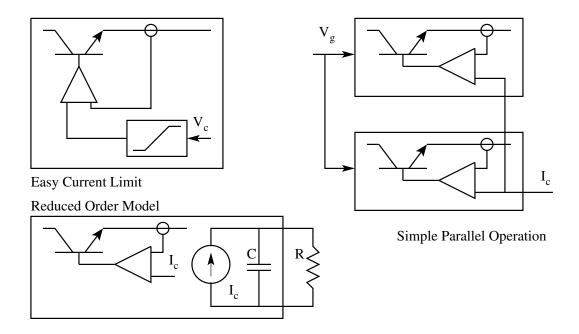

| <b>7</b> | Cur  | 0                                                          | 203 |

|          | 7.1  | Introduction                                               | 203 |

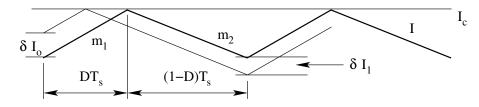

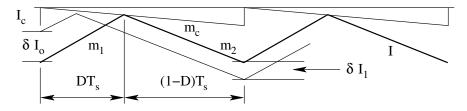

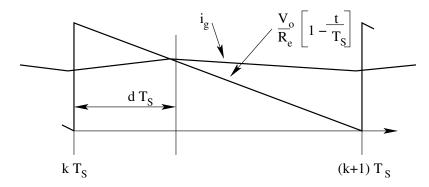

|          | 7.2  | Sub-harmonic Instability in Current Programmed Control     | 204 |

|          |      | 7.2.1 Compensation to Overcome Sub-harmonic Instability .  | 206 |

|          | 7.3  | Determination of Duty Ratio for Current Programmed Control | 207 |

|          |      | 7.3.1 Buck Converter                                       | 208 |

|          |      | 7.3.2 Boost Converter                                      | 208 |

|          |      | 7.3.3 Buck-Boost Converter                                 | 209 |

|          | 7.4  | Transfer Functions                                         | 209 |

|          |      | 7.4.1 Buck Converter                                       | 209 |

|          |      | 7.4.2 Boost Converter                                      | 212 |

|          |      |                                                            | 212 |

|          | 7.5  |                                                            | 214 |

|          |      |                                                            |     |

| 8        | Soft | 8                                                          | 217 |

|          | 8.1  |                                                            | 217 |

|          | 8.2  |                                                            | 218 |

|          |      | 1 1                                                        | 218 |

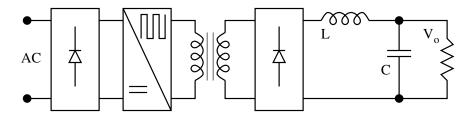

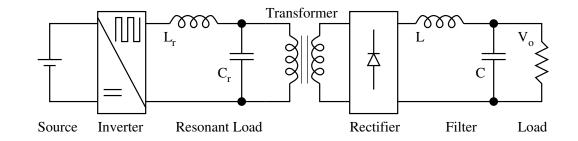

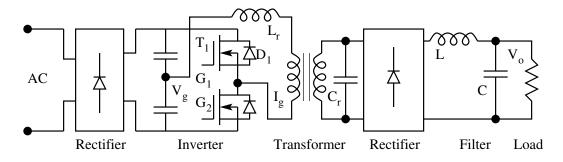

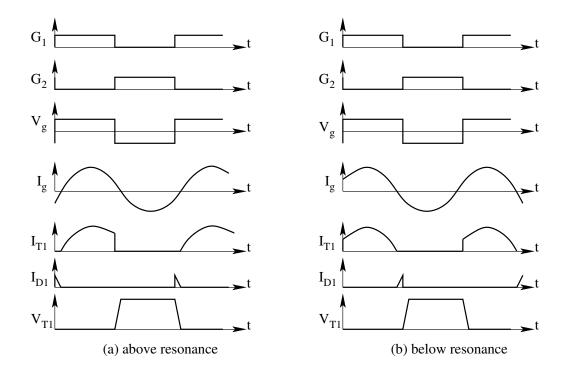

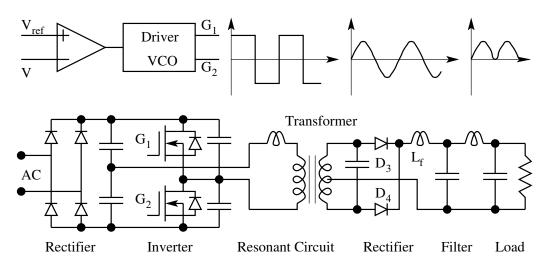

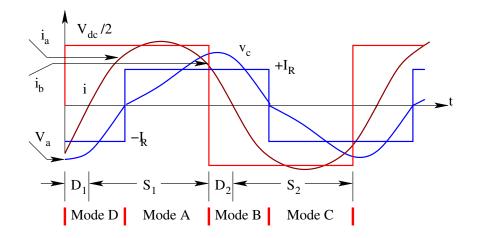

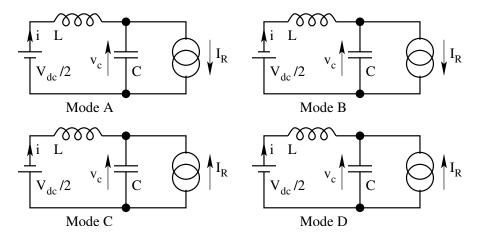

|          |      | 8.2.2 SMPS Using Resonant Circuit                          | 221 |

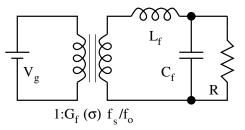

|   |     | 8.2.3   | Steady State Modeling of Resonant SMPS                                                                                                                                      | 225 |

|---|-----|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|   |     | 8.2.4   | Approximate Design Procedure                                                                                                                                                | 227 |

|   |     | 8.2.5   | Design Example                                                                                                                                                              | 229 |

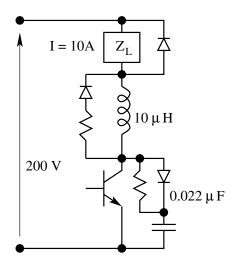

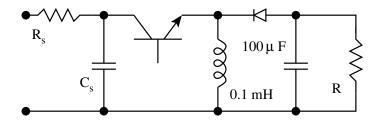

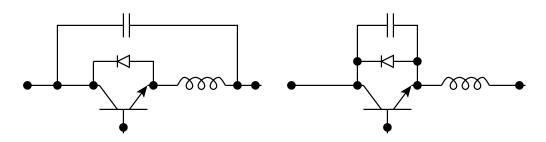

|   | 8.3 | Resona  | ant Switch Converters                                                                                                                                                       | 232 |

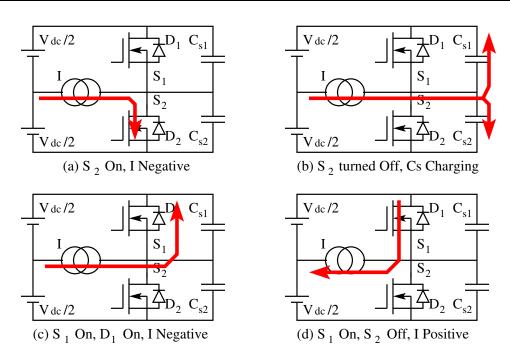

|   |     | 8.3.1   | Switch Realisation                                                                                                                                                          | 232 |

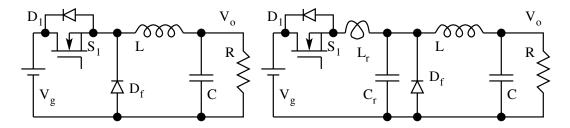

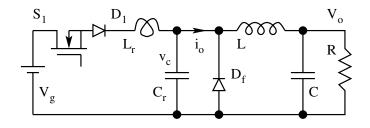

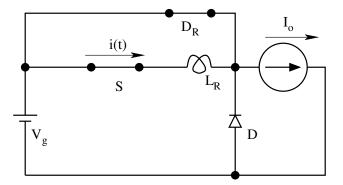

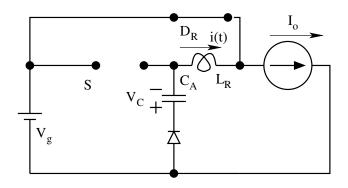

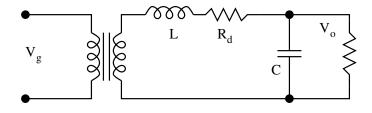

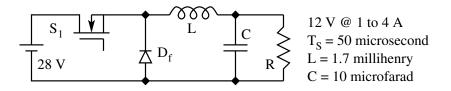

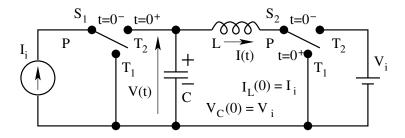

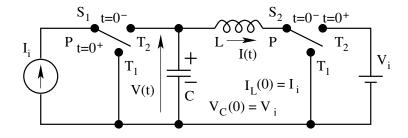

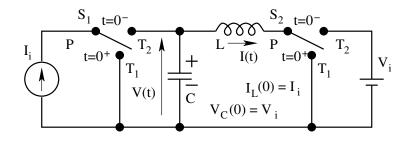

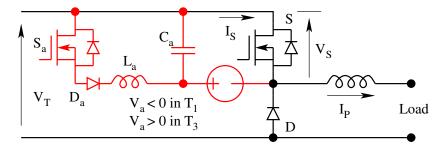

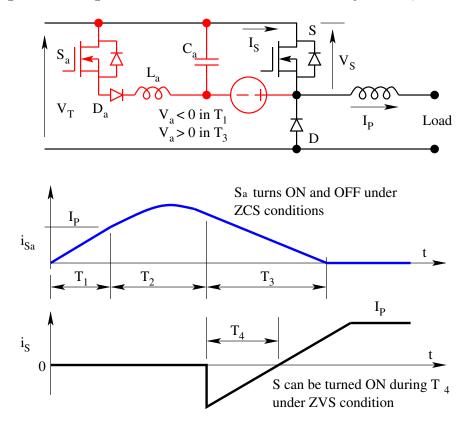

|   |     | 8.3.2   | Buck Converter with Zero Current Switching                                                                                                                                  | 233 |

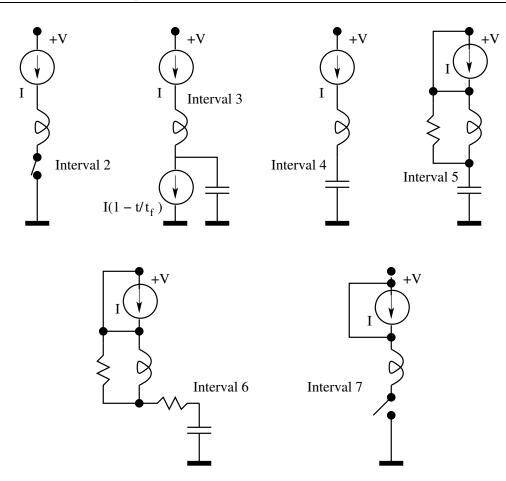

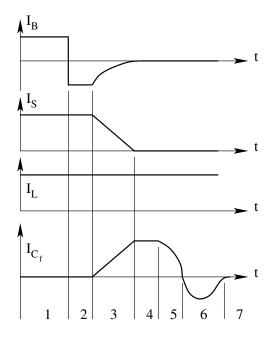

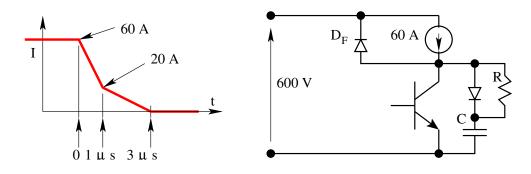

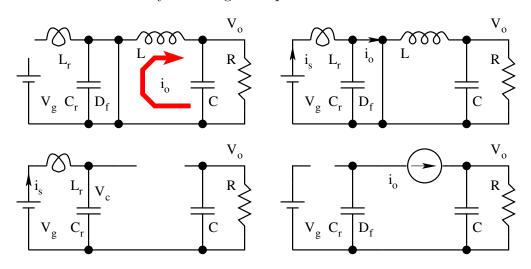

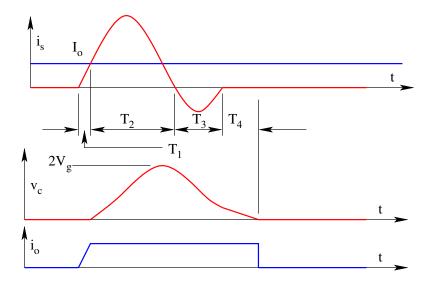

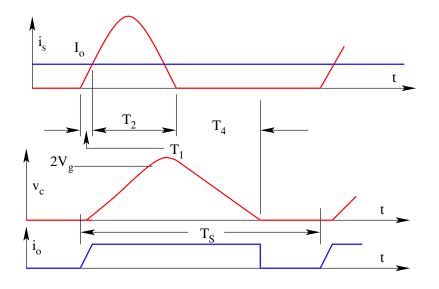

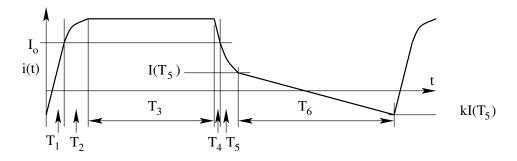

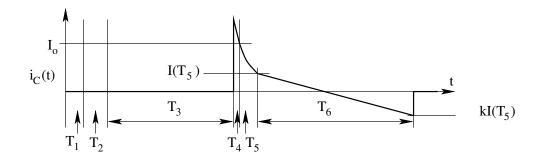

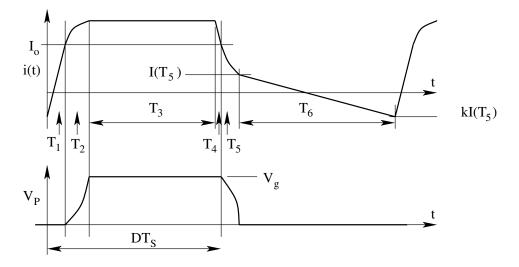

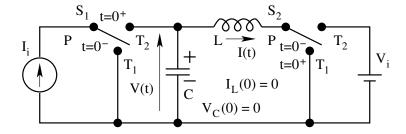

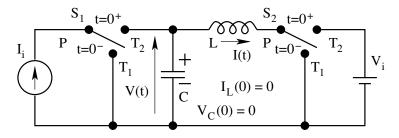

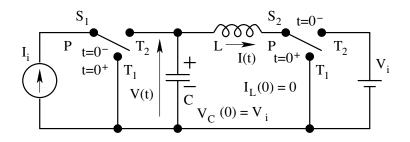

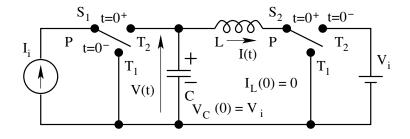

|   |     | 8.3.3   | Operation of the Circuit                                                                                                                                                    | 233 |

|   |     | 8.3.4   | Conversion Ratio of the Converter                                                                                                                                           | 236 |

|   |     | 8.3.5   | Halfwave Operation of the Converter                                                                                                                                         | 238 |

|   |     | 8.3.6   | Boost Converter with Zero Voltage Switching                                                                                                                                 | 239 |

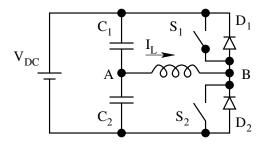

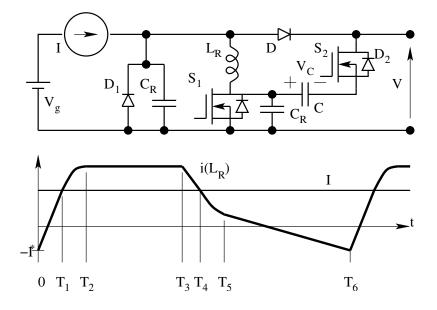

|   | 8.4 | Resona  | ant Transition Phase Modulated Converters                                                                                                                                   | 244 |

|   |     | 8.4.1   | Basic Principle of Operation                                                                                                                                                | 244 |

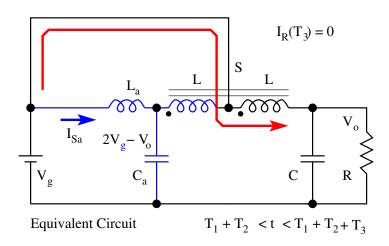

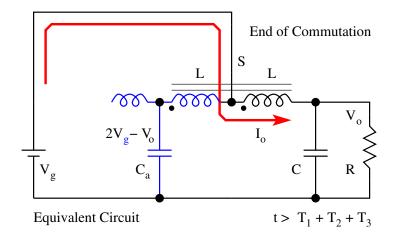

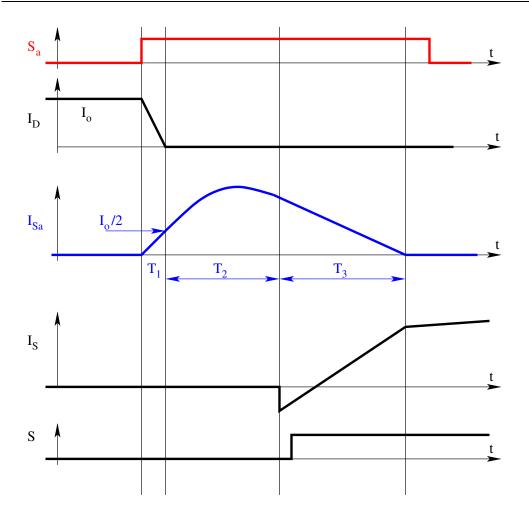

|   |     | 8.4.2   | Analysis of a complete cycle of operation                                                                                                                                   | 246 |

|   |     | 8.4.3   | Design considerations to achieve ZVS                                                                                                                                        | 249 |

|   |     | 8.4.4   | Development Examples                                                                                                                                                        | 251 |

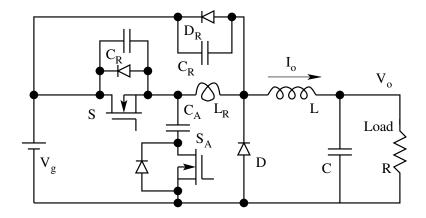

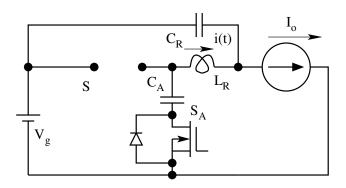

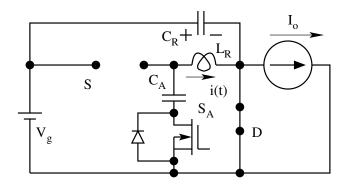

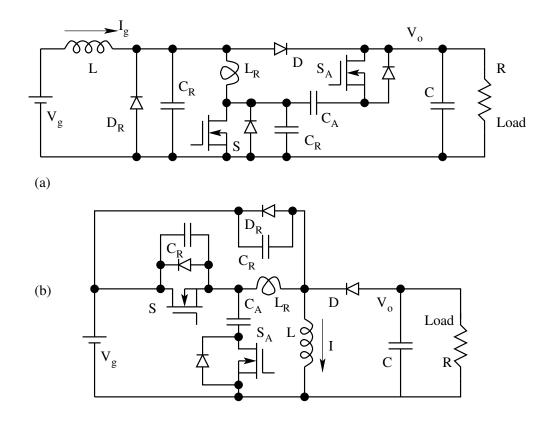

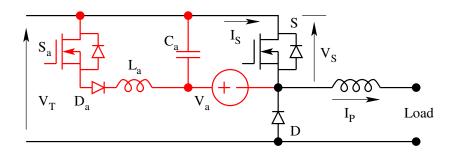

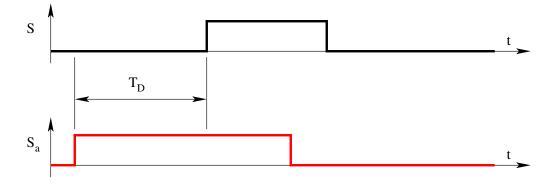

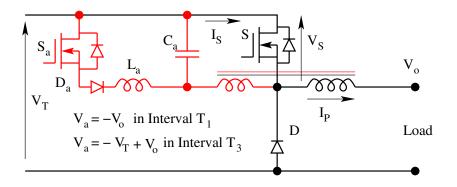

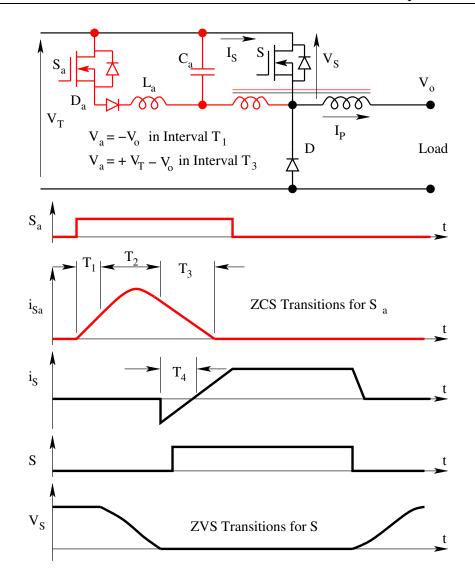

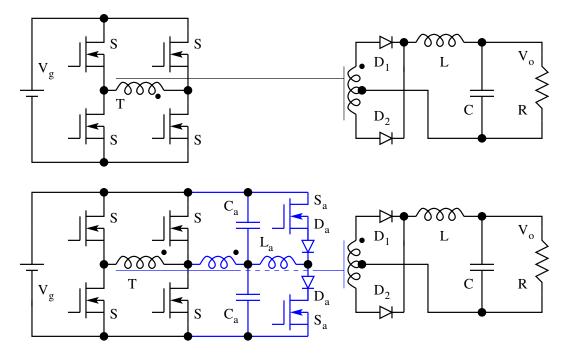

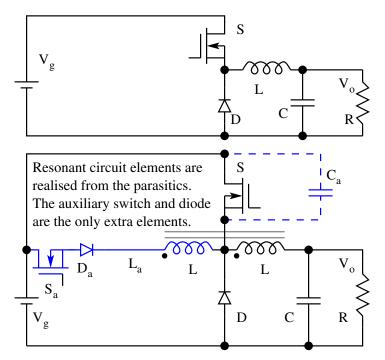

|   | 8.5 | Resona  | ant Switching Converters with Active Clamp                                                                                                                                  | 252 |

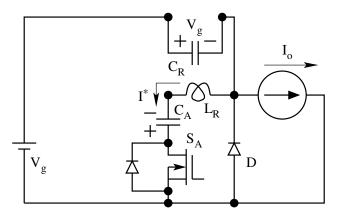

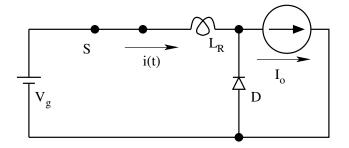

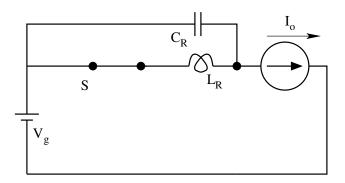

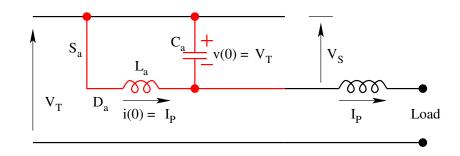

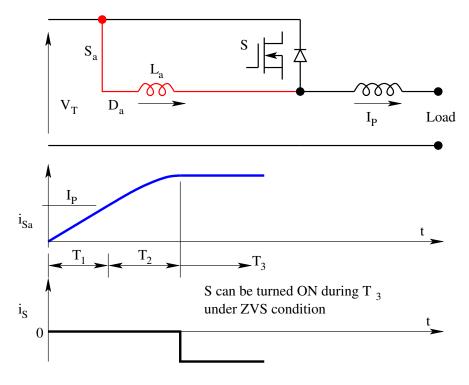

|   |     | 8.5.1   | Analysis of Active Clamp ZVS Buck Converter                                                                                                                                 | 253 |

|   |     | 8.5.2   | Steady State Conversion Ratio                                                                                                                                               | 260 |

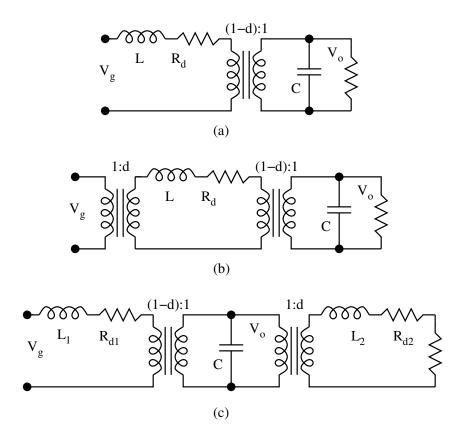

|   |     | 8.5.3   | Equivalent Circuit                                                                                                                                                          | 260 |

|   | 8.6 | Proble  | em Set                                                                                                                                                                      | 263 |

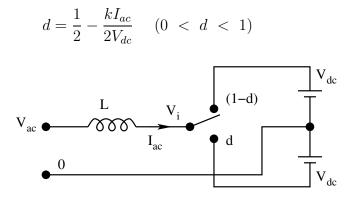

| 9 | Uni | tv Pow  | ver Factor Rectifiers                                                                                                                                                       | 265 |

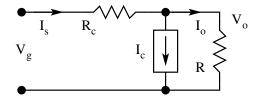

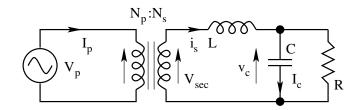

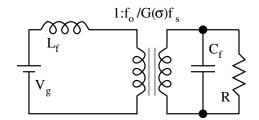

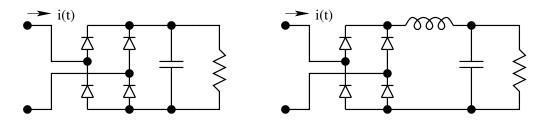

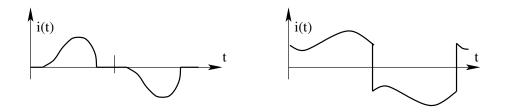

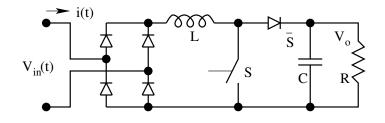

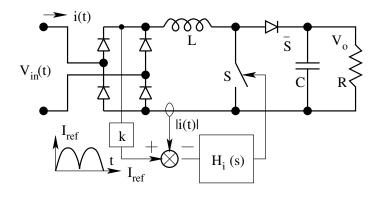

| 0 | 9.1 | •       | Circuit of UPF Rectifiers                                                                                                                                                   | 266 |

|   | 0.1 | 9.1.1   | Universal Input                                                                                                                                                             | 266 |

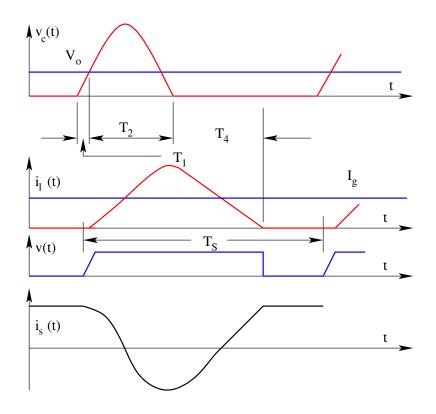

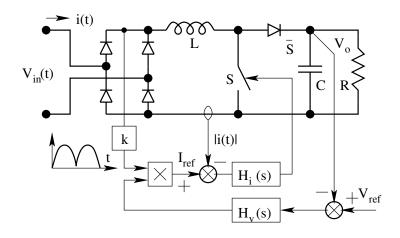

|   | 9.2 |         | ge Current Mode Control                                                                                                                                                     | 266 |

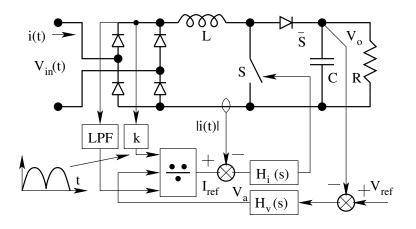

|   |     | 9.2.1   | Voltage Feedforward Controller                                                                                                                                              | 268 |

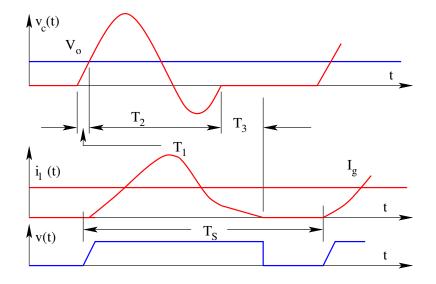

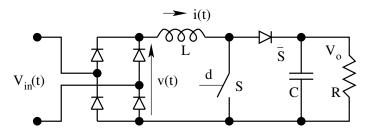

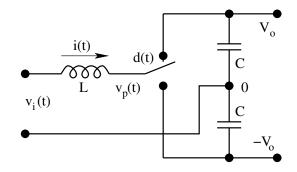

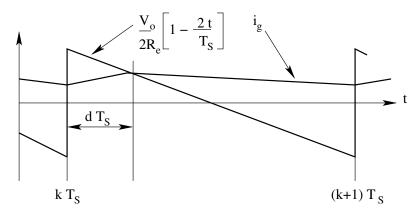

|   | 9.3 |         | or Emulator UPF Rectifiers                                                                                                                                                  | 268 |

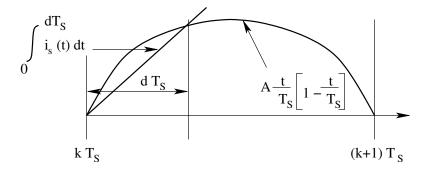

|   |     | 9.3.1   | Non-linear Carrier Control                                                                                                                                                  | 269 |

|   |     | 9.3.2   | Scalar Controlled Resistor Emulator                                                                                                                                         | 269 |

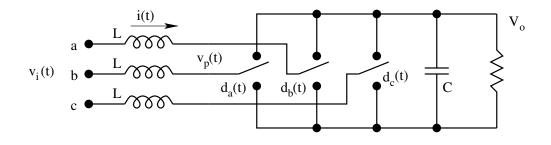

|   |     | 9.3.3   | Single Phase and Polyphase Rectifier                                                                                                                                        | 270 |

|   | 9.4 | Proble  | $\operatorname{em} \operatorname{Set} \ldots  | 272 |

| A | Rev | riew of | Control Theory                                                                                                                                                              | 273 |

|   |     |         | uction                                                                                                                                                                      | 273 |

|   |     | A.1.1   | System                                                                                                                                                                      | 273 |

|   |     | A.1.2   | Dynamic System                                                                                                                                                              | 274 |

|   |     | A.1.3   | Linear Dynamic System                                                                                                                                                       | 274 |

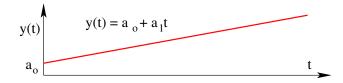

|   |     | A.1.4   | A Simple Linear System                                                                                                                                                      | 274 |

|   |     | A.1.5   | A Simple Linear Dynamic System                                                                                                                                              | 275 |

|   | A.2 | Laplac  | ce Transformation                                                                                                                                                           | 276 |

|   |     | A.2.1   | Transfer Function                                                                                                                                                           | 277 |

|   |     | A.2.2   | Physical Interpretation of the Transfer Function                                                                                                                            | 278 |

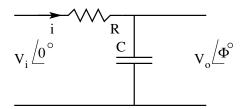

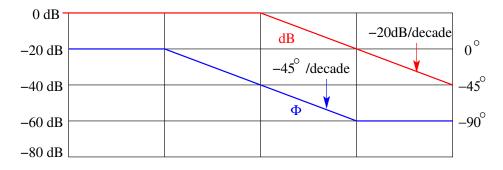

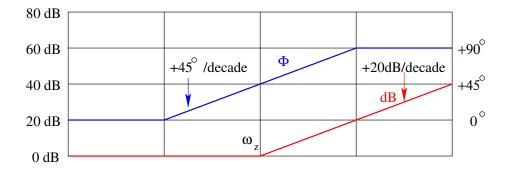

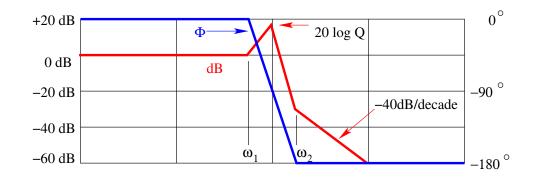

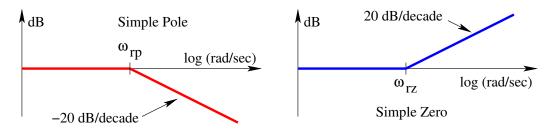

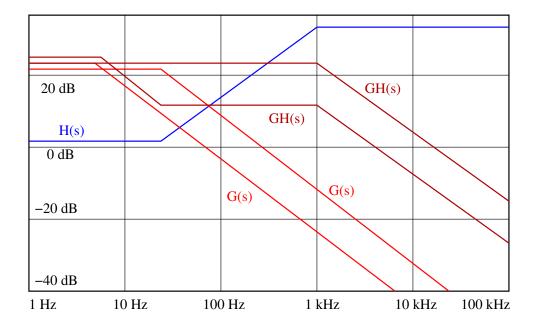

|   |     | A.2.3   | Bode Plots                                                                                                                                                                  | 278 |

|   |     | A.2.4   | Some Terminologies on Transfer Function                                                                                                                                     | 279 |

|   |     |         | G                                                                                                                                                                           |     |

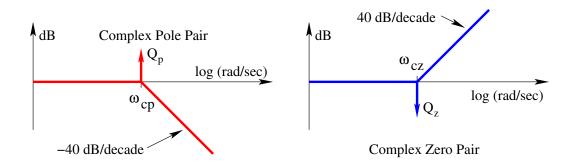

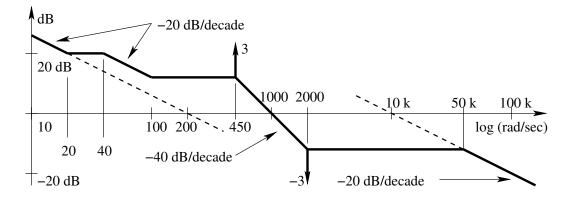

|    | A.2.5     | Asymptotic Bode Plots                             | 280 |

|----|-----------|---------------------------------------------------|-----|

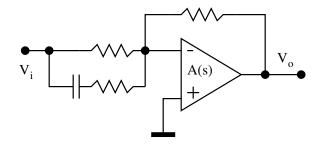

| A  | A.3 Princ | tiples of Closed Loop Control of Linear Systems   | 284 |

|    | A.3.1     | Effect of the Non ideal $G(s)$                    | 285 |

| ВE | Extra Ele | ement Theorem                                     | 287 |

| E  | B.1 Conc  | ept of Double Injection and Extra Element Theorem | 287 |

| E  |           | Application Examples                              | 290 |

|    | B.2.1     |                                                   | 290 |

|    | B.2.2     |                                                   | 291 |

|    | B.2.3     |                                                   | 291 |

|    | B.2.4     |                                                   | 292 |

| CF | Per Unit  | Description of Switched Mode Power Converters     | 295 |

| C  | C.1 Norm  | nalised Models of Switched Mode Power Converters  | 295 |

|    | C.1.1     | Normalisation                                     | 295 |

|    | C.1.2     | Dynamic Equations                                 | 295 |

|    | C.1.3     | Dynamic Equations in pu                           | 296 |

|    | C.1.4     | Some Sample Converters                            | 302 |

| C  | C.2 Prob  | lem Set                                           | 303 |

| DΝ | /isualisa | tion of Functions                                 | 305 |

| Ι  | D.1 Math  | nematical Functions                               | 305 |

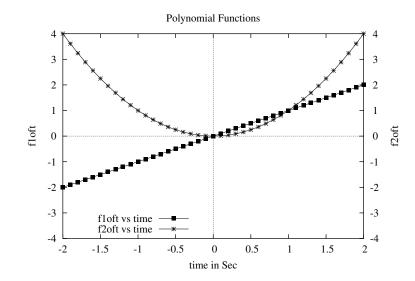

|    | D.1.1     | Polynomials                                       | 305 |

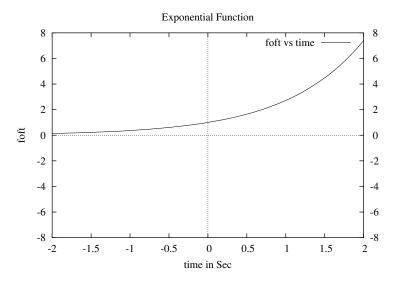

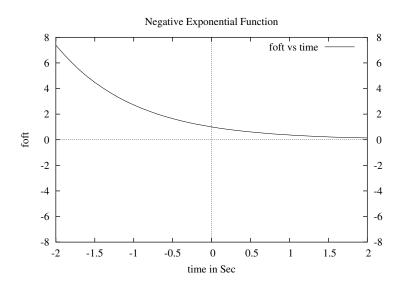

|    | D.1.2     | Exponential Function                              | 307 |

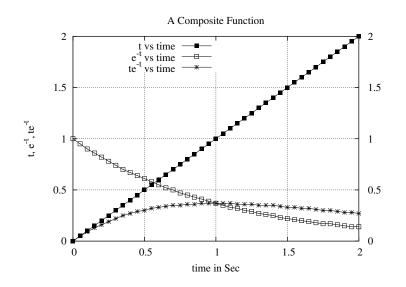

|    | D.1.3     | A Composite Function                              | 308 |

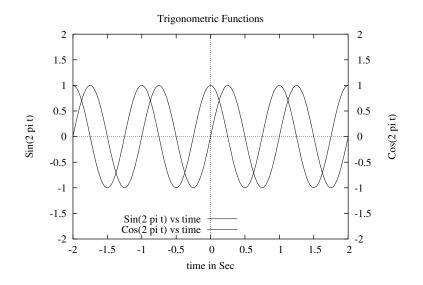

|    | D.1.4     |                                                   | 309 |

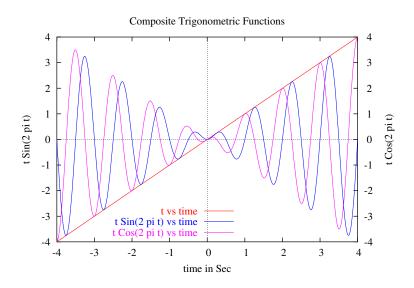

|    | D.1.5     | Composite Trigonometric Functions                 | 310 |

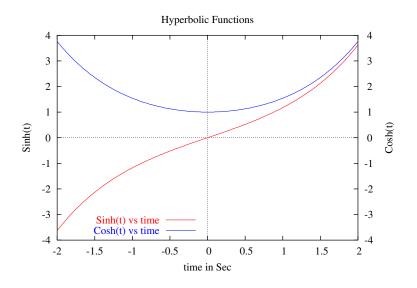

|    | D.1.6     | Hyperbolic Functions                              | 310 |

| Ι  | D.2 Func  | tions as Differential Equations                   | 311 |

|    | D.2.1     | Some Common Functions as Differential Equations   | 312 |

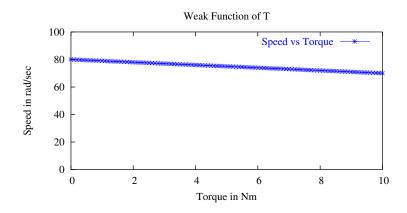

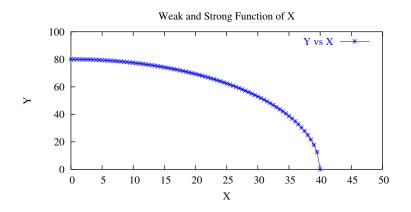

| Γ  | D.3 Stron | ng and Weak Functions                             | 314 |

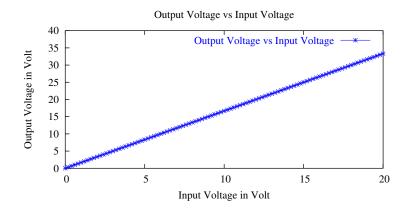

| Ι  | D.4 Linea | ar and Non-linear Functions                       | 316 |

| Ι  | D.5 Stead | ly-State and Dynamic Performance                  | 317 |

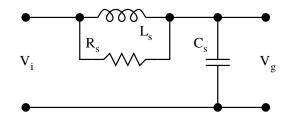

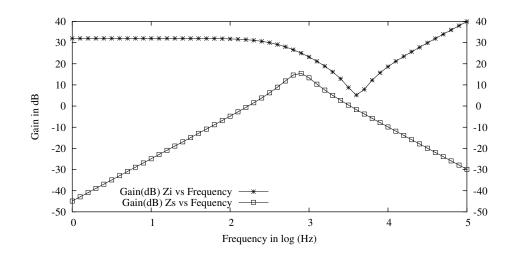

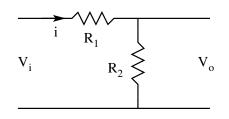

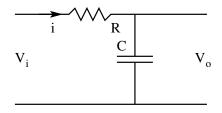

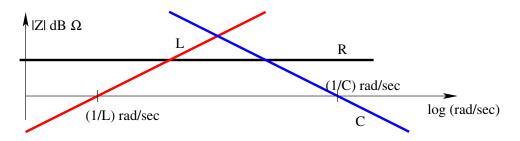

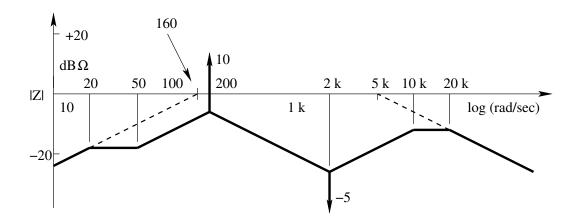

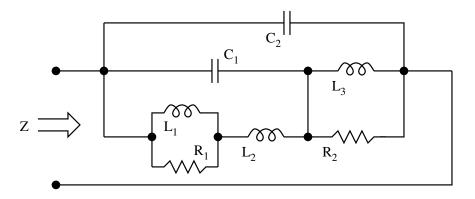

| Ι  | D.6 Impe  | dance Functions                                   | 318 |

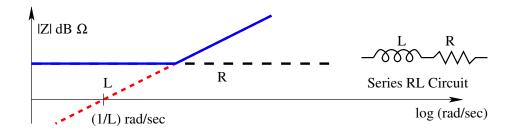

|    | D.6.1     | Series RL Circuit                                 | 319 |

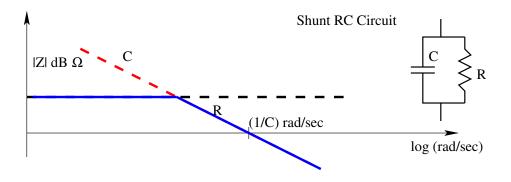

|    | D.6.2     | 2 Shunt RC Circuit                                | 319 |

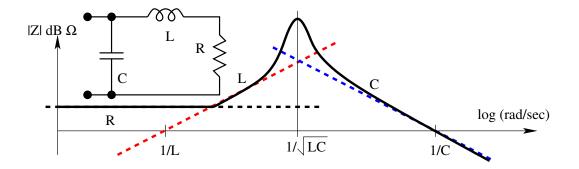

|    | D.6.3     | A Composite RLC Circuit                           | 319 |

| Ι  | D.7 Ratio | onal Polynomials                                  | 320 |

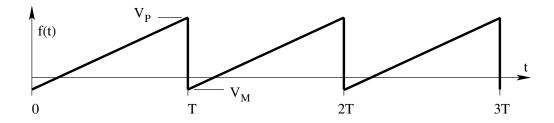

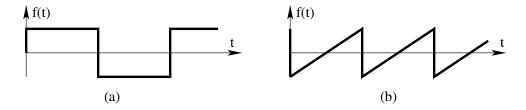

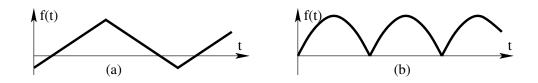

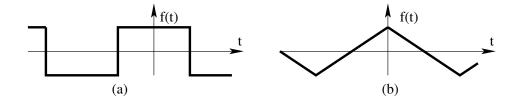

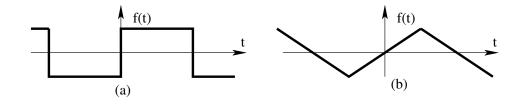

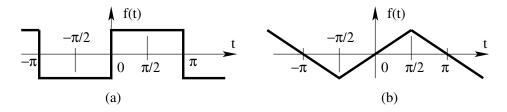

| Ι  | D.8 Perio | dic Functions                                     | 322 |

|    | D.8.1     | Certain Symmetries                                | 323 |

### CONTENTS

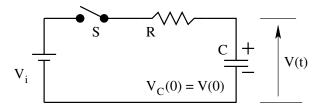

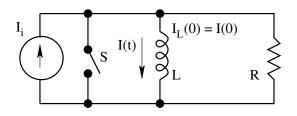

| E.2       Shunt RL Circuit       327         E.3       Series RL Circuit       328         E.4       Shunt RC Circuit       329         E.5       Series LC Circuit       329         E.6       Shunt LC Circuit       330         E.7       LC Circuit with Series and Shunt Excitation       331         E.7.1       LC Circuit with Initial Voltage       333         E.7.2       LC Circuit with Initial Current       335         E.7.3       LC Circuit with Initial Current       335         F.7.4       LC Circuit with Initial Current       335         F.7.4       LC Circuit with Initial Current       3341         F.2       A 250W Off-Line Forward Converter       341         F.2.1       Specifications       341         F.2.2       Selection of Input Capacitors       342         F.2.3       Power Circuit Topology       344         F.2.5       Output Inductor Selection       343         F.2.6       Output Capacitor Selection       343         F.2.7       Natural Frequencies of the Converter       344         F.2.8       Control Transfer Function       344         F.2.9       Compensator Design       345         F.2.10       <                                                                                                              | $\mathbf{E}$ | Tra | nsients | in Linear Electric Circuits                         | 327          |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|-----|---------|-----------------------------------------------------|--------------|

| E.3       Series RL Circuit       328         E.4       Shunt RC Circuit       329         E.5       Series LC Circuit       329         E.6       Shunt LC Circuit       330         E.7       LC Circuit with Series and Shunt Excitation       331         E.7.1       LC Circuit with Initial Voltage       333         E.7.2       LC Circuit with Initial Voltage       333         E.7.3       LC Circuit with Initial Voltage and Initial Current       337         F       Design Reviews       341         F.1       Introduction       341         F.2.1       Specifications       341         F.2.2       Selection of Input Capacitors       342         F.2.3       Power Circuit Topology       342         F.2.4       Transformer turns ratio       343         F.2.5       Output Inductor Selection       343         F.2.6       Output Capacitor Selection       344         F.2.7       Natural Frequencies of the Converter       344         F.2.8       Control Transfer Function       344         F.2.9       Compensator Design       345         F.2.10       Feedback Circuit       346         F.2.11       Control Power Supply                                                                                                                       |              | E.1 | Series  | RC Circuit                                          | 327          |

| E.4       Shunt RC Circuit       328         E.5       Series LC Circuit       329         E.6       Shunt LC Circuit with Series and Shunt Excitation       331         E.7       LC Circuit with Series and Shunt Excitation       331         E.7.1       LC Circuit with Zero Stored Energy       332         E.7.2       LC Circuit with Initial Current       335         E.7.3       LC Circuit with Initial Current       335         E.7.4       LC Circuit with Initial Current       337         F       Design Reviews       341         F.1       Introduction       341         F.2       A 2500W Off-Line Forward Converter       341         F.2.1       Specifications       342         F.2.3       Power Circuit Topology       342         F.2.4       Transformer turns ratio       343         F.2.5       Output Inductor Selection       343         F.2.6       Output Capacitor Selection       344         F.2.7       Natural Frequencies of the Converter       344         F.2.8       Control Transfer Function       344         F.2.9       Compensator Design       345         F.2.10       Fredueack Circuit       346         F.2.12                                                                                                              |              | E.2 | Shunt   | RL Circuit                                          | 327          |

| E.5       Series LC Circuit       329         E.6       Shunt LC Circuit with Series and Shunt Excitation       330         E.7       LC Circuit with Series and Shunt Excitation       331         E.7.1       LC Circuit with Initial Voltage       333         E.7.2       LC Circuit with Initial Voltage       333         E.7.3       LC Circuit with Initial Voltage and Initial Current       335         E.7.4       LC Circuit with Initial Voltage and Initial Current       337         F       Design Reviews       341         F.1       Introduction       341         F.2       A 250W Off-Line Forward Converter       341         F.2.1       Specifications       341         F.2.2       Selection of Input Capacitors       342         F.2.3       Power Circuit Topology       342         F.2.4       Transformer turns ratio       343         F.2.5       Output Inductor Selection       343         F.2.6       Output Capacitor Selection       344         F.2.7       Natural Frequencies of the Converter       344         F.2.8       Control Transfer Function       344         F.2.9       Compensator Design       345         F.2.10       Freduback Circuit <t< td=""><td></td><td>E.3</td><td>Series</td><td>RL Circuit</td><td>328</td></t<> |              | E.3 | Series  | RL Circuit                                          | 328          |

| E.6       Shunt LC Circuit       330         E.7       LC Circuit with Series and Shunt Excitation       331         E.7.1       LC Circuit with Zero Stored Energy       332         E.7.2       LC Circuit with Initial Voltage       333         E.7.3       LC Circuit with Initial Current       335         E.7.4       LC Circuit with Initial Current       337         F       Design Reviews       341         F.1       Introduction       341         F.2.1       Specifications       341         F.2.2       Selection of Input Capacitors       342         F.2.3       Power Circuit Topology       342         F.2.4       Transformer turns ratio       343         F.2.5       Output Inductor Selection       343         F.2.6       Output Capacitor Selection       344         F.2.7       Natural Frequencies of the Converter       344         F.2.8       Control Transfer Function       344         F.2.9       Compensator Design       345         F.2.10       Feedback Circuit       345         F.2.11       Control Power Supply       346         F.2.12       Switching Frequency       346         F.2.13       Soft Start <td></td> <td>E.4</td> <td>Shunt</td> <td>RC Circuit</td> <td>328</td>                                               |              | E.4 | Shunt   | RC Circuit                                          | 328          |

| E.7LC Circuit with Series and Shunt Excitation331E.7.1LC Circuit with Zero Stored Energy332E.7.2LC Circuit with Initial Voltage333E.7.3LC Circuit with Initial Current335E.7.4LC Circuit with Initial Current337FDesign Reviews341F.1Introduction341F.2A 250W Off-Line Forward Converter341F.2.1Specifications341F.2.2Selection of Input Capacitors342F.2.3Power Circuit Topology342F.2.4Transformer turns ratio343F.2.5Output Inductor Selection343F.2.6Output Capacitor Selection344F.2.7Natural Frequencies of the Converter344F.2.8Control Transfer Function344F.2.9Compensator Design345F.2.10Feedback Circuit345F.2.11Control Power Supply346F.2.12Switching Frequency346F.2.13Soft Start346F.2.14Drive circuits346F.2.15Dual Input Voltage Operation346F.2.16Snubber Circuit346F.2.17Current Controlled Push-Pull Converter347F.3.1Specifications347F.3.3Transformer Turns Ratio348F.3.4Transformer VA Rating348F.3.5Output Capacitor Selection348F.3.6Output Capacitor Selection348 <t< td=""><td></td><td>E.5</td><td>Series</td><td>LC Circuit</td><td>329</td></t<>                                                                                                                                                                                                         |              | E.5 | Series  | LC Circuit                                          | 329          |

| E.7.1       LC Circuit with Zero Stored Energy       332         E.7.2       LC Circuit with Initial Voltage       333         E.7.3       LC Circuit with Initial Current       335         E.7.4       LC Circuit with Initial Current       337         F       Design Reviews       341         F.1       Introduction       341         F.2       A 250W Off-Line Forward Converter       341         F.2.1       Specifications       341         F.2.2       Selection of Input Capacitors       342         F.2.3       Power Circuit Topology       342         F.2.4       Transformer turns ratio       343         F.2.5       Output Inductor Selection       343         F.2.6       Output Capacitor Selection       343         F.2.7       Natural Frequencies of the Converter       344         F.2.8       Control Transfer Function       344         F.2.9       Compensator Design       345         F.2.10       Feedback Circuit       345         F.2.11       Control Power Supply       346         F.2.12       Switching Frequency       346         F.2.13       Soft Start       346         F.2.14       Drive circuits       <                                                                                                                       |              | E.6 |         |                                                     | 330          |

| E.7.2       LC Circuit with Initial Voltage       333         E.7.3       LC Circuit with Initial Current       335         E.7.4       LC Circuit with Initial Voltage and Initial Current       337         F       Design Reviews       341         F.1       Introduction       341         F.2       A 250W Off-Line Forward Converter       341         F.2.1       Specifications       341         F.2.2       Selection of Input Capacitors       342         F.2.3       Power Circuit Topology       342         F.2.4       Transformer turns ratio       343         F.2.5       Output Inductor Selection       343         F.2.6       Output Capacitor Selection       343         F.2.7       Natural Frequencies of the Converter       344         F.2.8       Control Transfer Function       344         F.2.9       Compensator Design       345         F.2.10       Feedback Circuit       345         F.2.11       Control Power Supply       346         F.2.12       Switching Frequency       346         F.2.13       Soft Start       346         F.2.14       Drive circuits       346         F.2.15       Dual Input Voltage Operati                                                                                                                  |              | E.7 | LC Cir  | rcuit with Series and Shunt Excitation              | 331          |

| E.7.3       LC Circuit with Initial Current       335         E.7.4       LC Circuit with Initial Voltage and Initial Current       337         F       Design Reviews       341         F.1       Introduction       341         F.2       A 250W Off-Line Forward Converter       341         F.2.1       Specifications       341         F.2.2       Selection of Input Capacitors       342         F.2.3       Power Circuit Topology       342         F.2.4       Transformer turns ratio       343         F.2.5       Output Inductor Selection       343         F.2.6       Output Capacitor Selection       343         F.2.7       Natural Frequencies of the Converter       344         F.2.8       Control Transfer Function       344         F.2.9       Compensator Design       345         F.2.10       Feedback Circuit       345         F.2.11       Control Power Supply       346         F.2.12       Soft Start       346         F.2.13       Soft Start       346         F.2.14       Drive circuits       346         F.2.15       Dual Input Voltage Operation       346         F.2.16       Snubber Circuit       347 <th></th> <th></th> <th>E.7.1</th> <th>LC Circuit with Zero Stored Energy</th> <th>332</th>                                  |              |     | E.7.1   | LC Circuit with Zero Stored Energy                  | 332          |

| E.7.4LC Circuit with Initial Voltage and Initial Current.337FDesign Reviews341F.1Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |              |     | E.7.2   | 0                                                   |              |

| F       Design Reviews $341$ F.1       Introduction $341$ F.2       A 250W Off-Line Forward Converter $341$ F.2.1       Specifications $341$ F.2.2       Selection of Input Capacitors $342$ F.2.3       Power Circuit Topology $342$ F.2.4       Transformer turns ratio $343$ F.2.5       Output Inductor Selection $343$ F.2.6       Output Capacitor Selection $344$ F.2.7       Natural Frequencies of the Converter $344$ F.2.8       Control Transfer Function $344$ F.2.9       Compensator Design $345$ F.2.10       Feedback Circuit $345$ F.2.11       Control Power Supply $346$ F.2.12       Switching Frequency $346$ F.2.13       Soft Start $346$ F.2.14       Drive circuits $346$ F.2.15       Dual Input Voltage Operation $346$ F.2.16       Snubber Circuit $346$ F.2.17       Current Limit $346$ F.3.1       Specifications $347$                                                                                                                                                                                                                                                                                                                                                                                                                               |              |     | E.7.3   | LC Circuit with Initial Current                     | 335          |

| F.1       Introduction       341         F.2       A 250W Off-Line Forward Converter       341         F.2.1       Specifications       341         F.2.2       Selection of Input Capacitors       342         F.2.3       Power Circuit Topology       342         F.2.4       Transformer turns ratio       343         F.2.5       Output Inductor Selection       343         F.2.6       Output Capacitor Selection       344         F.2.7       Natural Frequencies of the Converter       344         F.2.8       Control Transfer Function       344         F.2.9       Compensator Design       345         F.2.10       Feedback Circuit       345         F.2.11       Control Transfer Function       344         F.2.9       Compensator Design       345         F.2.10       Feedback Circuit       346         F.2.12       Switching Frequency       346         F.2.13       Soft Start       346         F.2.14       Drive circuits       346         F.2.15       Dual Input Voltage Operation       346         F.2.16       Snubber Circuit       346         F.3.1       Specifications       347         <                                                                                                                                                 |              |     | E.7.4   | LC Circuit with Initial Voltage and Initial Current | 337          |

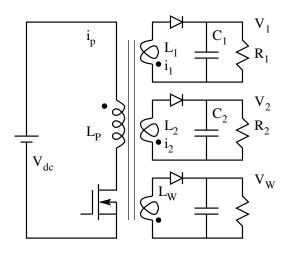

| F.2       A 250W Off-Line Forward Converter       341         F.2.1       Specifications       341         F.2.2       Selection of Input Capacitors       342         F.2.3       Power Circuit Topology       342         F.2.4       Transformer turns ratio       343         F.2.5       Output Inductor Selection       343         F.2.6       Output Capacitor Selection       343         F.2.7       Natural Frequencies of the Converter       344         F.2.8       Control Transfer Function       344         F.2.9       Compensator Design       345         F.2.10       Feedback Circuit       345         F.2.11       Control Tomore Supply       346         F.2.12       Switching Frequency       346         F.2.13       Soft Start       346         F.2.14       Drive circuits       346         F.2.15       Dual Input Voltage Operation       346         F.2.16       Snubber Circuit       346         F.2.17       Current Limit       346         F.2.18       Snubber Circuit       346         F.2.19       Dual Input Voltage Operation       346         F.3.1       Specifications       347 <t< td=""><td><math>\mathbf{F}</math></td><td>Des</td><td>ign Re</td><td>views</td><td>341</td></t<>                                            | $\mathbf{F}$ | Des | ign Re  | views                                               | 341          |

| F.2.1Specifications $341$ F.2.2Selection of Input Capacitors $342$ F.2.3Power Circuit Topology $342$ F.2.4Transformer turns ratio $343$ F.2.5Output Inductor Selection $343$ F.2.6Output Capacitor Selection $344$ F.2.7Natural Frequencies of the Converter $344$ F.2.8Control Transfer Function $344$ F.2.9Compensator Design $345$ F.2.10Feedback Circuit $345$ F.2.11Control Power Supply $346$ F.2.12Switching Frequency $346$ F.2.13Soft Start $346$ F.2.14Drive circuits $346$ F.2.15Dual Input Voltage Operation $346$ F.2.16Snubber Circuit $346$ F.2.17Current Limit $346$ F.2.17Current Controlled Push-Pull Converter $347$ F.3.1Specifications $347$ F.3.2Power Circuit $347$ F.3.3Transformer Turns Ratio $348$ F.3.4Transformer VA Rating $348$ F.3.5Output Inductor Selection $348$ F.3.6Output Capacitor Selection $349$ F.3.7Compensation Ramp $350$ F.3.8Closed Loop Control $350$ F.3.9Isolated Voltage Feedback $350$                                                                                                                                                                                                                                                                                                                                             |              | F.1 | Introd  | uction                                              | 341          |

| F.2.2Selection of Input Capacitors $342$ F.2.3Power Circuit Topology $342$ F.2.4Transformer turns ratio $343$ F.2.5Output Inductor Selection $343$ F.2.6Output Capacitor Selection $344$ F.2.7Natural Frequencies of the Converter $344$ F.2.8Control Transfer Function $344$ F.2.9Compensator Design $345$ F.2.10Feedback Circuit $345$ F.2.11Control Power Supply $346$ F.2.12Switching Frequency $346$ F.2.13Soft Start $346$ F.2.14Drive circuits $346$ F.2.15Dual Input Voltage Operation $346$ F.2.16Snubber Circuit $346$ F.2.17Current Limit $346$ F.3.1Specifications $347$ F.3.2Power Circuit $347$ F.3.3Transformer Turns Ratio $348$ F.3.4Transformer VA Rating $348$ F.3.5Output Inductor Selection $349$ F.3.6Output Capacitor Selection $349$ F.3.7Compensation Ramp $350$ F.3.8Closed Loop Control $350$ F.3.9Isolated Voltage Feedback $350$                                                                                                                                                                                                                                                                                                                                                                                                                          |              | F.2 | A 250V  | W Off-Line Forward Converter                        | 341          |

| F.2.3Power Circuit Topology $342$ F.2.4Transformer turns ratio $343$ F.2.5Output Inductor Selection $343$ F.2.6Output Capacitor Selection $344$ F.2.7Natural Frequencies of the Converter $344$ F.2.8Control Transfer Function $344$ F.2.9Compensator Design $345$ F.2.10Feedback Circuit $345$ F.2.11Control Power Supply $346$ F.2.12Switching Frequency $346$ F.2.13Soft Start $346$ F.2.14Drive circuits $346$ F.2.15Dual Input Voltage Operation $346$ F.2.16Snubber Circuit $346$ F.2.17Current Limit $346$ F.2.18Specifications $347$ F.3.1Specifications $347$ F.3.2Power Circuit $346$ F.3.3Transformer Turns Ratio $348$ F.3.4Transformer VA Rating $348$ F.3.5Output Inductor Selection $349$ F.3.6Output Capacitor Selection $349$ F.3.7Compensation Ramp $350$ F.3.8Closed Loop Control $350$ F.3.9Isolated Voltage Feedback $350$                                                                                                                                                                                                                                                                                                                                                                                                                                        |              |     | F.2.1   | Specifications                                      | 341          |

| F.2.4Transformer turns ratio343F.2.5Output Inductor Selection343F.2.6Output Capacitor Selection344F.2.7Natural Frequencies of the Converter344F.2.8Control Transfer Function344F.2.9Compensator Design345F.2.10Feedback Circuit345F.2.11Control Power Supply346F.2.12Switching Frequency346F.2.13Soft Start346F.2.14Drive circuits346F.2.15Dual Input Voltage Operation346F.2.16Snubber Circuit346F.2.17Current Limit346F.3.1Specifications347F.3.2Power Circuit347F.3.3Transformer Turns Ratio348F.3.4Transformer VA Rating348F.3.5Output Inductor Selection349F.3.7Compensation Ramp350F.3.8Closed Loop Control350F.3.9Isolated Voltage Feedback350                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |              |     | F.2.2   | Selection of Input Capacitors                       | 342          |

| F.2.5       Output Inductor Selection       343         F.2.6       Output Capacitor Selection       344         F.2.7       Natural Frequencies of the Converter       344         F.2.8       Control Transfer Function       344         F.2.9       Compensator Design       345         F.2.10       Feedback Circuit       345         F.2.11       Control Power Supply       346         F.2.12       Switching Frequency       346         F.2.13       Soft Start       346         F.2.14       Drive circuits       346         F.2.15       Dual Input Voltage Operation       346         F.2.16       Snubber Circuit       346         F.2.17       Current Limit       346         F.3.1       Specifications       347         F.3.2       Power Circuit       347         F.3.3       Transformer Turns Ratio       348         F.3.4       Transformer VA Rating       348         F.3.5       Output Inductor Selection       3                                                                                                                          |              |     | F.2.3   | Power Circuit Topology                              | 342          |

| F.2.6       Output Capacitor Selection       344         F.2.7       Natural Frequencies of the Converter       344         F.2.8       Control Transfer Function       344         F.2.9       Compensator Design       345         F.2.10       Feedback Circuit       345         F.2.11       Control Power Supply       346         F.2.12       Switching Frequency       346         F.2.13       Soft Start       346         F.2.14       Drive circuits       346         F.2.15       Dual Input Voltage Operation       346         F.2.16       Snubber Circuit       346         F.2.17       Current Limit       346         F.2.16       Snubber Circuit       346         F.2.17       Current Controlled Push-Pull Converter       347         F.3.1       Specifications       347         F.3.2       Power Circuit       347         F.3.3       Transformer Turns Ratio       348         F.3.4       Transformer VA Rating       348         F.3.5       Output Inductor Selection       349         F.3.7       Compensation Ramp       350         F.3.8       Closed Loop Control       350         F.3.9                                                                                                                                                    |              |     | F.2.4   | Transformer turns ratio                             | 343          |

| F.2.7       Natural Frequencies of the Converter       344         F.2.8       Control Transfer Function       344         F.2.9       Compensator Design       345         F.2.10       Feedback Circuit       345         F.2.11       Control Power Supply       346         F.2.12       Switching Frequency       346         F.2.13       Soft Start       346         F.2.14       Drive circuits       346         F.2.15       Dual Input Voltage Operation       346         F.2.16       Snubber Circuit       346         F.2.17       Current Limit       346         F.2.17       Current Limit       346         F.3.1       Specifications       347         F.3.2       Power Circuit       347         F.3.3       Transformer Turns Ratio       348         F.3.4       Transformer VA Rating       348         F.3.5       Output Inductor Selection       349         F.3.7       Compensation Ramp       350         F.3.8       Closed Loop Control       350         F.3.9       Isolated Voltage Feedback       350                                                                                                                                                                                                                                           |              |     | F.2.5   | Output Inductor Selection                           | 343          |

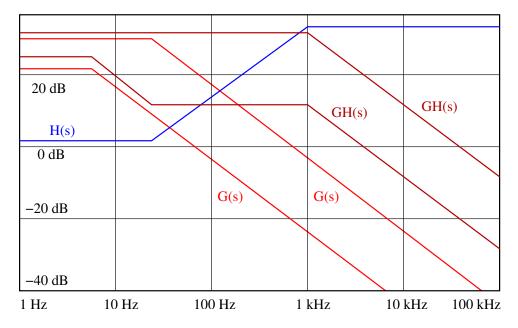

| F.2.8       Control Transfer Function       344         F.2.9       Compensator Design       345         F.2.10       Feedback Circuit       345         F.2.11       Control Power Supply       346         F.2.12       Switching Frequency       346         F.2.13       Soft Start       346         F.2.14       Drive circuits       346         F.2.15       Dual Input Voltage Operation       346         F.2.16       Snubber Circuit       346         F.2.17       Current Limit       346         F.2.17       Current Limit       346         F.2.17       Current Controlled Push-Pull Converter       347         F.3.1       Specifications       347         F.3.2       Power Circuit       347         F.3.3       Transformer Turns Ratio       348         F.3.4       Transformer VA Rating       348         F.3.5       Output Inductor Selection       349         F.3.6       Output Capacitor Selection       349         F.3.7       Compensation Ramp       350         F.3.8       Closed Loop Control       350                                                                                                                                                                                                                                       |              |     |         |                                                     |              |

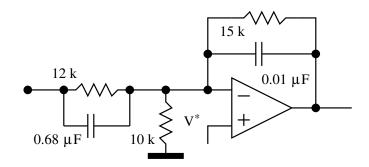

| F.2.9Compensator Design $345$ F.2.10Feedback Circuit $345$ F.2.11Control Power Supply $346$ F.2.12Switching Frequency $346$ F.2.13Soft Start $346$ F.2.14Drive circuits $346$ F.2.15Dual Input Voltage Operation $346$ F.2.16Snubber Circuit $346$ F.2.17Current Limit $346$ F.3.1Specifications $347$ F.3.2Power Circuit $347$ F.3.3Transformer Turns Ratio $348$ F.3.4Transformer VA Rating $348$ F.3.5Output Inductor Selection $349$ F.3.7Compensation Ramp $350$ F.3.8Closed Loop Control $350$ F.3.9Isolated Voltage Feedback $350$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |              |     |         | -                                                   |              |

| F.2.10Feedback Circuit $345$ F.2.11Control Power Supply $346$ F.2.12Switching Frequency $346$ F.2.13Soft Start $346$ F.2.14Drive circuits $346$ F.2.15Dual Input Voltage Operation $346$ F.2.16Snubber Circuit $346$ F.2.17Current Limit $346$ F.2.17Current Controlled Push-Pull Converter $347$ F.3.1Specifications $347$ F.3.2Power Circuit $347$ F.3.3Transformer Turns Ratio $348$ F.3.4Transformer VA Rating $348$ F.3.5Output Inductor Selection $349$ F.3.7Compensation Ramp $350$ F.3.8Closed Loop Control $350$ F.3.9Isolated Voltage Feedback $350$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |              |     | -       |                                                     |              |

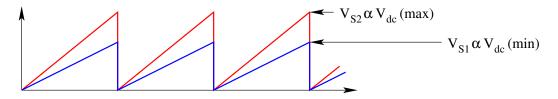

| F.2.11       Control Power Supply       346         F.2.12       Switching Frequency       346         F.2.13       Soft Start       346         F.2.13       Soft Start       346         F.2.14       Drive circuits       346         F.2.15       Dual Input Voltage Operation       346         F.2.16       Snubber Circuit       346         F.2.17       Current Limit       346         F.3       A 500W Current Controlled Push-Pull Converter       347         F.3.1       Specifications       347         F.3.2       Power Circuit       347         F.3.3       Transformer Turns Ratio       348         F.3.4       Transformer VA Rating       348         F.3.5       Output Inductor Selection       348         F.3.6       Output Capacitor Selection       349         F.3.7       Compensation Ramp       350         F.3.8       Closed Loop Control       350         F.3.9       Isolated Voltage Feedback       350                                                                                                                                                                                                                                                                                                                                       |              |     |         |                                                     |              |

| F.2.12Switching Frequency346F.2.13Soft Start346F.2.14Drive circuits346F.2.15Dual Input Voltage Operation346F.2.16Snubber Circuit346F.2.17Current Limit346F.3A 500W Current Controlled Push-Pull Converter347F.3.1Specifications347F.3.2Power Circuit347F.3.3Transformer Turns Ratio348F.3.4Transformer VA Rating348F.3.5Output Inductor Selection349F.3.7Compensation Ramp350F.3.8Closed Loop Control350F.3.9Isolated Voltage Feedback350                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |              |     |         |                                                     |              |

| F.2.13 Soft Start       346         F.2.14 Drive circuits       346         F.2.15 Dual Input Voltage Operation       346         F.2.15 Dual Input Voltage Operation       346         F.2.16 Snubber Circuit       346         F.2.17 Current Limit       346         F.3 A 500W Current Controlled Push-Pull Converter       347         F.3.1 Specifications       347         F.3.2 Power Circuit       347         F.3.3 Transformer Turns Ratio       348         F.3.4 Transformer VA Rating       348         F.3.5 Output Inductor Selection       349         F.3.6 Output Capacitor Selection       349         F.3.7 Compensation Ramp       350         F.3.8 Closed Loop Control       350         F.3.9 Isolated Voltage Feedback       350                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |              |     |         |                                                     |              |

| F.2.14 Drive circuits346F.2.15 Dual Input Voltage Operation346F.2.16 Snubber Circuit346F.2.17 Current Limit346F.3 A 500W Current Controlled Push-Pull Converter347F.3.1 Specifications347F.3.2 Power Circuit347F.3.3 Transformer Turns Ratio348F.3.4 Transformer VA Rating348F.3.5 Output Inductor Selection349F.3.6 Output Capacitor Selection349F.3.7 Compensation Ramp350F.3.8 Closed Loop Control350F.3.9 Isolated Voltage Feedback350                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |              |     |         |                                                     |              |

| F.2.15 Dual Input Voltage Operation346F.2.16 Snubber Circuit346F.2.17 Current Limit346F.3 A 500W Current Controlled Push-Pull Converter347F.3.1 Specifications347F.3.2 Power Circuit347F.3.3 Transformer Turns Ratio348F.3.4 Transformer VA Rating348F.3.5 Output Inductor Selection349F.3.6 Output Capacitor Selection349F.3.7 Compensation Ramp350F.3.8 Closed Loop Control350F.3.9 Isolated Voltage Feedback350                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |              |     |         |                                                     |              |

| F.2.16Snubber Circuit346F.2.17Current Limit346F.3A 500W Current Controlled Push-Pull Converter347F.3.1Specifications347F.3.2Power Circuit347F.3.3Transformer Turns Ratio348F.3.4Transformer VA Rating348F.3.5Output Inductor Selection349F.3.7Compensation Ramp350F.3.8Closed Loop Control350F.3.9Isolated Voltage Feedback350                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |              |     |         |                                                     |              |

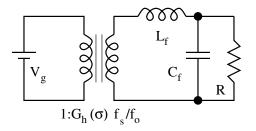

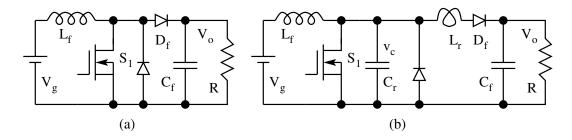

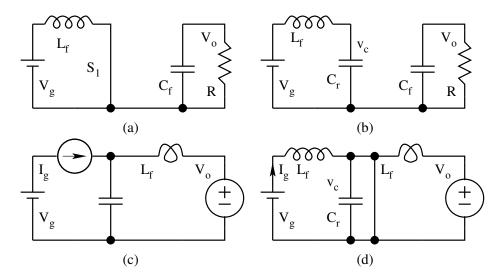

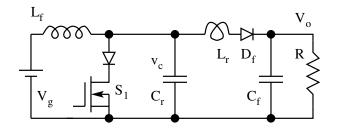

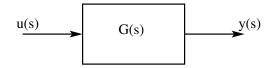

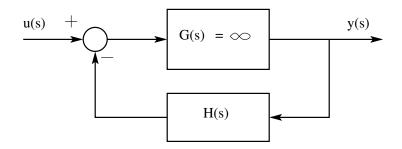

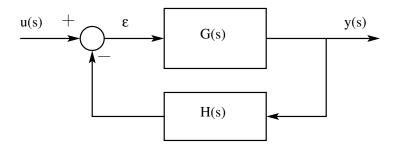

| F.2.17 Current Limit346F.3 A 500W Current Controlled Push-Pull Converter347F.3.1 Specifications347F.3.2 Power Circuit347F.3.3 Transformer Turns Ratio348F.3.4 Transformer VA Rating348F.3.5 Output Inductor Selection348F.3.6 Output Capacitor Selection349F.3.7 Compensation Ramp350F.3.8 Closed Loop Control350F.3.9 Isolated Voltage Feedback350                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |              |     |         |                                                     |              |